## 17<sup>th</sup> International Conference Reliability and Stress-Related Phenomena in Nanoelectronics

"Stress workshop"

Abstract booklet

April, 24 – April, 26, 2023 Bad Schandau, Germany

Sponsors:

# 17<sup>th</sup> International Conference Reliability and Stress-Related Phenomena in Nanoelectronics

## Scope

More than ever before, materials-driven product innovations in semiconductor industry and shorter time-to-market introductions for new micro- and nanoelectronic products require high advancement rates and tight coupling between research, development and manufacturing. Since novel product design and process steps, and particularly the integration of new materials, require the understanding of stress-related phenomena to ensure the requested product lifetime, reliability physics and engineering as well as materials engineering and nano-scale materials characterization are considered as fundamental drivers for innovation in semiconductor industry.

Traditionally, this series of conferences has been focused on stress arising in micro- and nanoscale structures of on-chip interconnect stacks and advanced packaging structures. This thermomechanical stress can lead to degradation phenomena such as crack propagation caused by chip-package interaction and to the acceleration of known reliability-limiting processes in backend-of-line stacks such as electromigration and time-dependent dielectric breakdown. The 17th conference will include two new focus areas:

- Reliability at harsh environments (e.g. space, automotive),

- Materials behavior and reliability of organic and flexible electronics

The conference will cover the whole range from fundamental research to industrial applications. It will provide a forum for scientists and engineers from universities, research institutions and industry to discuss current challenges and future scenarios related to reliability and stress-induced phenomena in micro- and nanoelectronics.

## **Co-Chairs:**

- Ehrenfried Zschech, deepXscan Dresden & Technische Universität Dresden, Germany

- Reiner Dauskardt, Stanford University, Palo Alto/CA, USA

- Valeriy Sukharev, Mentor Graphics / Siemens EDA, Fremont/CA, USA

- Olivier Thomas, Aix-Marseille Universite, France

- Zhong Chen, NTU Singapore

## Venue:

Hotel Elbresidenz Bad Schandau near Dresden, Germany

## **Organizational committee**

Dominik Gronarz, Organic Electronics Saxony, Dresden, Germany Kristina Kutukova, deepXscan GmbH, Dresden, Germany Johann Zeller, student, Dresden, Germany Kim Brendel, Hotel Elbresidenz, Bad Schandau, Germany

## Contact / Help:

Kristina Kutukova Mobile phone: +491733969207

Symposium management Organic Electronics Saxony Cluster

## Topics of the conference

- Stress-related issues for advanced nonvolatile memories, including embedded phasechange memory

- Materials behavior at low temperatures for quantum computing, reliability-related aspects

- Scaling limitations of materials

- Role of microstructure and interfaces on mechanical behaviour of nanostructures

- Stress and thermal effects in advanced packaging, heterogeneous integration, and chip-package interaction

- Thermo-mechanical properties and stress: Measurements and simulation

- Advanced characterization techniques

- Compact modeling and statistical methods in circuit/device life-time assessment

- Thermal and stress-driven floor-planning methodology, stress mitigation techniques, and design technology co-optimization

- Reliability physics and engineering, damage and failure mechanisms

- Stability and lifetime of organic and flexible electronics

- Lifetime and ageing of nanoscale materials, structures and systems at low and high temperatures

- Component (device / interconnect) reliability vs. system reliability

- Reliability of products at harsh environments

- Reliability of power devices

## Highlights

- Podium discussion "Reliability of automotive electronics" with Andreas Aal (VOLKSWAGEN) and Oliver Aubel (GLOBALFOUNDRIES)

- Hiking tour in Saxonian Switzerland

- 2 Poser sessions and 3 best poster awards

- Conference dinner

- Lab tour at deepXscan

## **Session Chairs:**

- Ehrenfried Zschech, deepXscan Dresden & Technische Universität Dresden, Germany

- Carl V. Thompson, MIT, Boston/NY, USA

- Reiner Dauskardt, Stanford University, Palo Alto/CA, USA

- Christoph Gammer, ESI Leoben, Austria

- Rodrigo Martins, Uninova Lisabon, Portugal

- André Clausner, Fraunhofer IKTS Dresden, Germany

- Olivier Thomas, Aix-Marseille Universite, France

- Kristina Kutukova, deepXscan Dresden, Germany

## **Scientific Committee:**

- Alex Dommann, EMPA, Switzerland

- Martin Gall, GLOBALFOUNDRIES Malta/NY, USA

- Chee Lip Gan, NTU Singapore

- Goeran Jerke, Bosch Stuttgart, Germany

- Junichi Koike, Tohoku University, Sendai, Japan

- Jens Lienig, Technical University Dresden, Germany

- Zhiyong Ma, Intel, Hillsboro/OR, USA

- Jon Molina, IMDEA Materials, Madrid, Spain

- Stephane Moreau, Leti Grenoble, France

- Luu Nguyen, Psi Quantum, Palo Alto/CA, USA

- Natalia Sobczak, IMIM PAN Cracow, Poland

- Oden Warren, Bruker, Minneapolis/MN, USA

- Ingrid de Wolf, IMEC Leuven, Belgium

- Xiaopeng Xu, Synopsys, Mountain View/CA, USA

## **Invited Speakers:**

- André Clausner, Fraunhofer IKTS Dresden, Germany

- Carl V. Thompson, MIT, Boston/NY, USA

- Christoph Gammer, ESI Leoben, Austria

- Daniel Nemecek, TESCAN Brno, Czech Republic

- Ehrenfried Zschech, deepXscan Dresden, Germany

- Hiroshi Nishikawa, Osaka University, Japan

- Ingrid de Wolf, IMEC Leuven, Belgium

- Iuliana Panchenko, Technische Universität Dresden, Germany

- Jörg Acker, Brandenburg University of Technology Cottbus-Senftenberg, Germany

- Karl Leo, Technische Universität Dresden, Germany

- Kristina Kutukova, deepXscan Dresden, Germany

- Lionel Vignoud, CEA-LETI Grenoble, France

- Matthias Stecher, Infineon Technologies, Munich, Germany

- Olivier Thomas, Aix Marseille Universitem Marseille, France

- Pal-Jen Wei, Bruker, Taiwan

- Reinhold Dauskardt, Stanford University Palo Alto/CA, USA

- Robert Filipek, AGH Krakow, Poland

- Rodrigo Martins, Uninova Lisabon, Portugal

- Sandrine Lhostis, ST Microelectronics Crolles, France

- Susann Rothe, Technical University Dresden, Germany

- Vikas Tapan, Siemens, Munich, Germany

- Wiebke Langgemach, Fraunhofer FEP, Dresden, Germany

## Program

10:30 – 11:00 Break

## Monday 24th April 2023

|      |            |                                                                                                                                                                                                | · ·                                                                                                                                                       |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |            | Chair: Ehrenfried Zschech                                                                                                                                                                      | Session 1: Reliability in micro- and nanoelectronics                                                                                                      |

|      | 08:45      | Ehrenfried Zschech<br>deepXscan, Dresden, Germany                                                                                                                                              | Opening remarks                                                                                                                                           |

| T1   | 09:00      | Sandrine Lhostis<br>STMicroelectronics, France                                                                                                                                                 | New reliability challenges for 3D integration stacking using hybrid bonding                                                                               |

| Т2   | 09:30      | Susann Rothe<br>Technical University Dresden, Germany                                                                                                                                          | Combined Modeling of Electromigration, Thermal and Stress Migration in AC Interconnect Lines                                                              |

| Т3   | 10:00      | Ingrid de Wolf, Vladimir Chairman<br>IMEC, Leuven, Belgium                                                                                                                                     | FinFETs: Sensing and feeling mechanical stress                                                                                                            |

| 10:3 | 80 - 11:00 | Break                                                                                                                                                                                          |                                                                                                                                                           |

|      |            | Chair: Carl V. Thompson                                                                                                                                                                        | Session 2: Impact of stress on device properties                                                                                                          |

| Т4   | 11:00      | Kristina Kutukova<br>deepXscan, Dresden, Germany                                                                                                                                               | In-situ nano-XCT study of the local energy release rate for crack propagation in advanced ICs                                                             |

| Т5   | 11:30      | Pal Jen Wie<br>Bruker, Taiwan                                                                                                                                                                  | Indentation-Induced Delamination and Adhesion Work Evaluation at Elevated Temperature in Semicon Indus-<br>trial Cases                                    |

| Т6   | 12:00      | André Clausner<br>Fraunhofer IKTS, Dresden, Germany                                                                                                                                            | Studying stress effects in transistor channels by nanoindentation with varied contact geometries                                                          |

| Т7   | 12:30      | Reinhold Dauskardt<br>Stanford University, Palo Alto/CA, USA                                                                                                                                   | Hybrid Dielectric Films for Device Technologies: Understanding Relationships between Molecular Structure, Pro-<br>cessing and Function                    |

| 13:0 | 0 - 14:30  | Lunch Break                                                                                                                                                                                    |                                                                                                                                                           |

|      |            | Chair: Reinhold Dauskardt                                                                                                                                                                      | Session 3: Robustness of engineered systems: From design to application                                                                                   |

| Т8   | 14:30      | Vikas Tapan<br>Siemens, Munich, Germany                                                                                                                                                        | Early architectural exploration with PAVE360                                                                                                              |

| Т9   | 15:00      | Hiroshi Nishikawa<br>Osaka University, Japan                                                                                                                                                   | Solid-phase bonding process using nanostructured surface for power devices in automotive                                                                  |

|      | 15:30      | Chair: Kristina Kutukova                                                                                                                                                                       | Poster Session                                                                                                                                            |

|      | 17:00      | Moderators:<br>Andreas Aal, VOLKSWAGEN<br>Oliver Aubel, GLOBALFOUNDRIES<br>Key Contributors:<br>Joe McPherson<br>Günter Haas (Entegris)<br>Tapan Vikas (SiemensEDA)<br>Nir Sever (proteanTecs) | <b>Podium discussion "Reliability of automotive electronics"</b><br>Context: Upcoming hardware challenges on the way towards the Software-defined-Vehicle |

| :    | 19:00      | BBQ                                                                                                                                                                                            |                                                                                                                                                           |

|      |            |                                                                                                                                                                                                |                                                                                                                                                           |

## Tuesday 25th April 2023

|     | Chair: Christoph Gammer |                                                            | Session 4: Materials characterization for device development and reliability engineering                                     |

|-----|-------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| T10 | 09:00                   | Iuliana Panchenko<br>Technical University Dresden, Germany | Hybrid bond and nanowired bump technologies for high density interconnect formation on wafer level                           |

| T11 | 09:30                   | Olivier Thomas,<br>Aix Marseille University, France        | Phase change materials for embedded memories: in situ investigation of crystalli-zation behavior using synchrotron radiation |

| T12 | 10:00                   | Ehrenfried Zschech,<br>deepXscan, Dresden, Germany         | Controlled microcrack steering into toughened regions – What microelectronics can learn from nature?                         |

|     |                         |                                                            |                                                                                                                              |

|     |       | Chair: Rodrigo Martins                                                             | Session 5: Degradation mechanisms and materials behaviour                                                                |

|-----|-------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| T13 | 11:00 | Matthias Stecher<br>Infineon Technologies, Munich, Germany                         | Degradation mechanisms of 10kV-reinforced isolated gate drivers at high switching frequencies greater than 30kHz         |

| T14 | 11:30 | Carl V. Thompson<br>MIT, Boston/NY, USA                                            | Contrasting Stress Evolution During Lithiation and Delithiation of Different Electrode Materials for Thin Film Batteries |

| T15 | 12:00 | Robert Filipek<br>AGH Krakow, Poland                                               | Tortuosity and Porosity in Electrochemical Systems – Computed Tomography Based 3D Transport Modelling                    |

| T16 | 12:30 | Jörg Acker<br>Brandenburg University of Technology<br>Cottbus-Senftenberg, Germany | Reliability and Recycling of Battery Materials                                                                           |

| 13:00 - 14:00 | Lunch Break                         |                |

|---------------|-------------------------------------|----------------|

| 14:00         | Hiking tour in Saxonian Switzerland |                |

| 17:30         | Chair: Kristina Kutukova            | Poster session |

| 20:00         | Conference Dinner                   |                |

## Wednesday 26th April 2023

|            |                | Chair: André Clausner                                                                                            | Session 6: Micro- and nanomechanics                                                                                                  |

|------------|----------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| T17        | 09:00          | Lionel Vignoud<br>CEA-LETI, Grenoble, France                                                                     | Strains and stresses control in microelectronic devices: How to optimize the steps from design to manufactur-<br>ing?                |

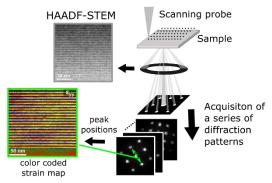

| T18        | 09:30          | Daniel Nemecek<br>TESCAN, Brno, Czech Republic                                                                   | Advancing nanoscale characterization of semiconductor devices by effortless 4D-STEM workflows                                        |

| T19        | 10:00          | Christoph Gammer,<br>ESI Leoben, Austria                                                                         | Recent advances in nanoscale strain mapping using 4D STEM                                                                            |

| 10:3       | 0 - 11:00      | Break                                                                                                            |                                                                                                                                      |

|            |                | Chair: Olivier Thomas                                                                                            | Session 7: Reliability of organic electronics                                                                                        |

|            |                |                                                                                                                  |                                                                                                                                      |

| T20        | 11:00          | Rodrigo Martins<br>Uninova Lisbon, Portugal                                                                      | Eco-Strategies for next generation electronics                                                                                       |

| T20<br>T21 | 11:00<br>11:30 | Rodrigo Martins                                                                                                  |                                                                                                                                      |

|            |                | Rodrigo Martins<br>Uninova Lisbon, Portugal<br>Wiebke Langgemach                                                 | Eco-Strategies for next generation electronics                                                                                       |

| T21        | 11:30          | Rodrigo Martins<br>Uninova Lisbon, Portugal<br>Wiebke Langgemach<br>Fraunhofer FEP, Dresden, Germany<br>Karl Leo | Eco-Strategies for next generation electronics<br>Processing flexible glass – thin film stress and its influence on glass durability |

### **Poster session**

Monday, 24th April 2023 15:30 and Tuesday, 25th April 2023 17:30

| Poster | Author                    | Title                                                                                                                          |

|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|

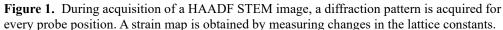

| P1     | Susann Rothe              | A Proactive Design Approach to Avoid Migration-Induced Failure in IC Interconnects                                             |

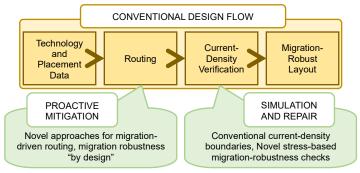

| P2     | Verena Hein               | The Influence of the Interconnect Material on the Performance of a Highly Robust Metallization Layout                          |

| Р3     | Stefan Weitz              | Micromechanical in-situ studies of on-chip interconnect stack structures using X-ray microscopy                                |

| P4     | Michael Reisinger         | Characterization of the thermo-mechanical behavior of Cu metallization in microelectronic applications                         |

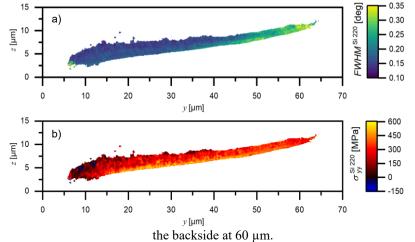

| P5     | Tobias Ziegelwanger       | Local gradients of microstructure and residual stresses in Si device sidewalls separated by laser dicing                       |

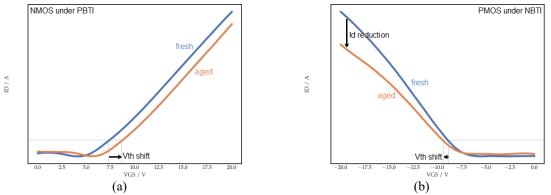

| P6     | André Lange               | Investigating HCI and BTI degradation in 4H-SiC CMOS                                                                           |

| P7     | Jolanta Janczak-Rusch     | Nanomultilayers for thermal management and micro-/nano-joining                                                                 |

| P8     | Bastian Rheingans         | Thin-film transfer by nanopaste sinter-bonding                                                                                 |

| Р9     | Bowen Zhang               | In-situ TEM study and nanomechanical characterization of fracture behavior in two-dimensional covalent organic frame-<br>works |

| P10    | Thomas Langner/Jörg Acker | Shaping the topography of solar wafers due to increased reactivity of lattice strained silicon                                 |

| P11    | Thomas Langner/Jörg Acker | Deposition of copper in lithium-ion batteries during the deep discharge process                                                |

| P12    | Thomas Langner/Jörg Acker | Degradation of Cathode Foils from Lithium-Ion Batteries in Humid Atmosphere                                                    |

## **Invited Talks and Posters**

## Contents

Invited talks:

| <b>T1: S. Lhostis,</b> New reliability challenges for 3D integration stacking using hybrid bonding12                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T2: S. Rothe, Combined Modeling of Electromigration, Thermal and Stress Migration                                                                          |

| in AC Interconnect Lines                                                                                                                                   |

| T3: I. De Wolf, FinFETS: Sensing and feeling mechanical stress                                                                                             |

| <b>T4: K. Kutukova,</b> In-situ nano-XCT study of the local energy release rate for crack propagation in advanced ICs                                      |

| <b>T5: P. Wei</b> Indentation-induced delamination and adhesion work evaluation at elevated temperature in industrial semiconductors                       |

| <b>T6: A. Clausner,</b> Piezoresistive Characteristics of MOSFET Channels Determined with Indentation Stress-induced Ring Oscillator Parameter Shifts      |

| <b>T7: R. Dauskardt,</b> Hybrid Dielectric Films for Device Technologies: Understanding Relationships between Molecular Structure, Processing and Function |

| <b>T9: H. Nishikawa,</b> Solid-phase bonding process using nanostructured surface for power devices in automotive                                          |

| <b>T10: I. Panchenko,</b> Hybrid bond and nanowired bump technologies for high density interconnect formation on wafer level                               |

| <b>T11: O. Thomas,</b> Phase change materials for embedded memories: <i>in situ</i> investigation of crystallization behavior using synchrotron radiation  |

| <b>T12: E. Zschech,</b> Controlled microcrack steering into toughened regions – What microelectronics can learn from nature?                               |

| <b>T13: M. Stecher,</b> Degradation mechanisms of 10kV-reinforced isolated gate drivers at high switching frequencies greater than 30kHz                   |

| <b>T14: C. Thompson,</b> Contrasting Stress Evolution During Lithiation and Delithiation of Different Electrode Materials for Thin Film Batteries          |

| <b>T15: R. Filipek,</b> Tortuosity and Porosity in Electrochemical Systems - Computed Tomography Based 3D Transport Modelling                              |

| T16: J. Acker, Reliability and Recycling of Battery Materials                                                                                              |

| <b>T17: L.Vignout,</b> Strains and stresses control in microelectronic devices: how to optimize the steps from design to manufacturing ?                   |

| <b>T18: D. Němeček,</b> Advancing nanoscale characterization of semiconductor devices by effortless 4D-STEM workflows                                      |

| T19: C. Gammer, Recent advances in nanoscale strain mapping using 4D STEM                                                                                  |

| T20: R. Martins, Eco Strategies for Next Generation Electronics                                                                                            |

| <b>T21: W. Langgemach,</b> Processing flexible glass – thin film stress and its influence on glass durability                                              |

| <b>T22: K. Leo,</b> Organic semiconductors - from a lab curiosity to serious applications                                                                  |

| 9                                                                                                                                                          |

## Posters:

| P1: S. Rothe, A Proactive Design Approach to Avoid Migration-Induced Failure in IC<br>Interconnects                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>P2: V. Hein,</b> The Influence of the Interconnect Material on the Performance of a Highly Robust Matallization Layout                             |

| <b>P3: S. Weitz,</b> Micromechanical in-situ studies of on-chip interconnect stack structures using X-ray microscopy                                  |

| <b>P4: M. Reisinger,</b> Characterization of the thermo-mechanical behavior of Cu metallization in microelectronic applications                       |

| <b>P5: T. Ziegelwanger,</b> Local gradients of microstructure and residual stresses in Si device sidewalls separated by laser dicing                  |

| P6: A. Lange, Investigating HCI and BTI degradation in 4H-SiC CMOS                                                                                    |

| P7: J. Janczak-Rusch, Nanomultilayers for thermal management and micro-/nano-joining 40                                                               |

| <b>P8: B. Rheingans,</b> Thin-film transfer by nanopaste sinter-bonding41                                                                             |

| <b>P9: B. Zhang,</b> <i>In-situ</i> TEM study and nanomechanical characterization of fracture behavior in two-dimensional covalent organic frameworks |

| <b>P10: T. Langner/ J. Acker,</b> Shaping the topography of solar wafers due to increased reactivity of lattice strained silicon                      |

| <b>P11: T. Langner/ J. Acker,</b> Deposition of copper in lithium-ion batteries during the deep discharge process                                     |

| <b>P12: T. Langner/ J. Acker,</b> Degradation of Cathode Foils from Lithium-Ion Batteries in Humid Atmosphere                                         |

Abstracts -Invited Talks-

## New reliability challenges for 3D integration stacking using hybrid bonding

Sandrine Lhostis<sup>1</sup>\*, Bassel Ayoub<sup>1,2,3</sup>, Stéphane Moreau<sup>3</sup>, Patrick Lamontagne<sup>1</sup>, Hélène Frémont<sup>2</sup>

<sup>1</sup>STMicroelectronics: 850 rue Jean Monnet, F-38926 Crolles Cedex, France <sup>2</sup>IMS Laboratory: University of Bordeaux, UMR 5218, 33405 Talence, France <sup>3</sup>CEA-Leti: Univ. Grenoble Alpes, F-38000 Grenoble, France

#### \*sandrine.lhostis@st.com

Improving efficiency and performance is the main driver for microelectronic applications. The new trend named beyond Moore's law refers to the emergence of new architectures, processes, devices and materials [1]. 3D stacking is definitely an enabler for new architectures and packaging. During the last ten years, many demonstrations were done showing that stacking dies of different technologies enable new functionalities for optical sensor, memories and CPU devices [2-3]. Increasing the interconnect number by reducing the interconnection pitch between top and bottom tiers is key to get faster devices. Hybrid bonding, based on oxide-to-oxide and metal-to-metal direct bonding between the reported tiers, is a path for one of the most scalable integrations. We are interested here in the robustness of the hybrid bonding level when decreasing the interconnection pitch below submicrometric dimensions. The different features for reliability requirements are reviewed and discussed towards standard Back-End-Of-Line interconnects robustness.

Many integration flows have been developed for hybrid bonding stacking. The most critical integration scheme in terms of potential metal diffusion is based on a hybrid bonding interface made of silicon oxide and copper. We have developed a specific integration that is immune to copper diffusion into the faced oxide. This interface stability is assessed towards potential atomic and ionic diffusion [4]. The integrity of the hybrid bonding interface towards Cu diffusion is confirmed by dedicated Time Dependent Dielectric Breakdown studies through a novel test method. A different dependence between time-to-failure and electrical field is observed for the Cu/SiO<sub>2</sub> hybrid bonding configuration than for standard BEOL interconnects [5]. Another potential concern for a device is the repetitive thermomechanical stresses that could lead to interface delamination in the case of hybrid bonding integration. With pitch reduction, higher stress is expected at the bonding level due to the reduced spacing between the pads. This point is assessed by Thermal Cycling tests for pitch reduction [6]. Stress induced Voiding (SiV) may also be a concern. This failure mechanism is driven by the grain microstructure. In our developed integration, reducing the bonding pad size leads to the modification of the copper microstructure from polycrystalline to one-grain-dominant feature [7]. However, no modification of the robustness to SiV is identified even for bonding pad width reduced to 300nm [8]. Reliability under electron flow and thermal stress is performed through electromigration tests. Previous studies on large interconnect pitch have shown that the hybrid bonding level behaves as a standard BEOL level with failure occurring in the feeding lines. With sub-micron pad width reduction, a modification in the failure mechanism is identified. The extracted lifetime is still in line with the specifications [9].

In-depth studies on the  $Cu/SiO_2$  hybrid bonding level indicate that this specific integration is robust to standard failure mechanisms for wafer -to-wafer interconnect pitch down to 710nm and pad width of 300 nm.

#### Acknowledgments

This work has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826600 (project VIZTA). This work was also supported by the cooperative Research & Development program "IPCEI, Nano 2022 and by the French National Research Agency (ANR) under the "Investissements d'avenir" programs: ANR 10-AIRT-0005 (IRT NANO-ELEC).

#### References

- [1] L. Xiu et al., *IEEE Solid-State Circuits Magazine* **2019**, *11(1)*, 39.

- [2] Y. Oike et al., IEEE Transactions on electron devices 2022, 69 (6), 2757.

- [3] S. Moreau et al., ECS Journal of Solid State Science and Technology 2022, 11(2), 024001.

- [4] B. Ayoub et al., Microelectronic Reliability, 2023, 114934.

- [5] B. Ayoub et al., IEEE International Reliability Physics Symposium (IRPS) 2022, 4C.3-1

- [6] J. Jourdon et al., IEEE International Electron Devices Meeting (IEDM) 2018, 7.3.1.

- [7] B. Ayoub et al., Microelectronic Engineering 2022, 261, 111809.

- [8] B. Ayoub et al., IEEE 24th Electronics Packaging Technology Conference (EPTC) 2022, 418.

[9] S. Moreau et al., IEEE International Reliability Physics Symposium (IRPS) 2023, to be presented

## Combined Modeling of Electromigration, Thermal and Stress Migration in AC Interconnect Lines

#### Susann Rothe\*, Jens Lienig

### Dresden University of Technology, Institute of Electromechanical and Electronic Design, 01062 Dresden, Germany, www.ifte.de

#### \*susann.rothe@mailbox.tu-dresden.de

The migration of atoms in metal interconnects in integrated circuits (ICs) increasingly endangers chip reliability. The susceptibility of DC interconnects to electromigration has been extensively studied. A few works on thermal migration and AC electromigration are also available. Yet, the combined effect of both on chip reliability has been neglected thus far.

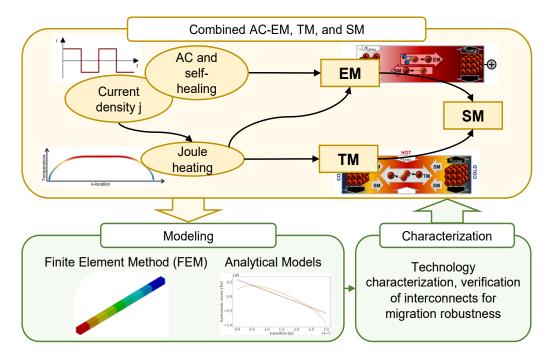

This talk introduces both FEM and analytical models for atomic migration and steady-state stress profiles *in AC interconnects* considering electromigration, thermal and stress migration (EM, TM, and SM) *combined*. For this we expand existing models by the impact of self-healing, temperature-dependent resistivity, and short wire length. We conclude by analyzing the impact of thermal migration on interconnect robustness and show that it cannot be neglected any longer in migration-robustness verification.

Figure 1 illustrates our novel methodology which has been published in [1].

Figure 1. Illustration of the interactions of EM, TM, and SM (top) and the contribution of this talk (bottom). As shown on the lower left, we provide both FEM and analytical models which can be the basis for experimental technology characterization, migration robustness verification, and novel design strategies to mitigate migration-induced failures (lower right).

#### Reference

[1] S. Rothe, J. Lienig, "Combined Modeling of Electromigration, Thermal and Stress Migration in AC Interconnect Lines," *Proc. of the ACM 2023 Int. Symposium on Physical Design*, pp. 107–114, **2023**.

## **FinFETS: Sensing and feeling mechanical stress**

Ingrid De Wolf<sup>1,2</sup>\*, Vladimir Cherman<sup>1</sup>

<sup>1</sup>imec, Remiseboslaan 1, 3001 Leuven, Belgium <sup>2</sup>Dept. Materials Science, Fac. Engineering Science, KU Leuven, Leuven, Belgium

#### \*ingrid.dewolf@imec.be

The impact of mechanical stress (MS) on mobility in Si and Ge, through the piezoresistivity effect, was already described in 1954 [1]. In 1991 first publications appeared discussing the impact of MS on MOSFET reliability [2,3]. MS was shown to affect hot-carrier degradation, which is directly related to its impact on mobility. With the advent of 3D-technology in the 21<sup>st</sup> century, there came an increasing concern that TSV-induced stress affects the nearby transistors, indicating the need for a 'keep-out zone' around the TSV, where no transistors should be placed [4,5]. Also chip-stacking and packaging induced mechanical stress effects on transistors raised concerns [6]. This was referred to as 'chip-package interaction (CPI)'. Over the years several researchers at imec studied the interaction between mechanical stress and FETs, either focusing on their sensitivity, or using them as sensors [3-8]. This talk presents an overview of the main results.

To study the impact of TSVs on FETs, dedicated test structures with transistors placed at different positions from the TSV were used. This allowed to determine the keep-out zone. It was found that the piezoresistive factors proposed by Smith [1] could not be used for these new technologies. It was also shown that stress-impact due to TSVs could be described using Lame's equation [5]. While for planar FETs n-type is less sensitive to mechanical stress than p-type, this is not the case for FinFETS, both types are sensitive.

While all these studies initially focused on in-plane stress, the question raised about the impact of vertical stress. This was studied using a nanoindenter set-up in combination with in-situ electrical probing [7]. These experiments showed a clear impact of vertical stress in FinFETs [8], but also indicated that nanoindentation produced both in-plane and out-of-plane stress, and in these experiments FEM models were required to calibrate the stress. A nice solution to this was offered by Schlipf et al. [9,10].

#### Acknowledgments

All imec contributors and partners of the 3D program of imec are acknowledged. Especially all design and processing engineers providing samples, all stress-impact researchers, and the program director Eric Beyne

#### References

- [1] C. S. Smith, Phys. Rev. 1954, 94(42)

- [2] A. Hamada et al. IEEE Transaction on Electron Devices 1991, 38(4), 895-900.

- [3] R. Degraeve et al. Proc. IEEE (IRPS) 1994, 29-33.

- [4] A. Mercha et al. 2010 Proc. Int. Electron Devices Meet. (IEDM) 2010, 2.2.1-2.2.4

- [5] W. Guo et al. Proc. IEEE Int. Conf. IC Design Technol. 2012, 1-4

- [6] V. Cherman et al. Proc. IEEE Electronic Components & Technology CoNference (ECTC) 2014, 309-315.

- [7] Liu Y. et al. 2018 Proc. Int. Electron Devices Meet. (IEDM) 2018, 17.7.1–17.7.2.

- [8] T. Furuhashi et al. Proc. 22nd European Microelectronics and Packaging Conference (EMPC) 2019

[9] S. Schlipf et al. IEEE Transactions on device and materials reliability 2021, 21(10), 9-16

[10] S. Schlipf PhD Thesis, TU Dresden, 2021

## In-situ nano-XCT study of the local energy release rate for crack propagation in advanced ICs

Kristina Kutukova<sup>1</sup>\*, Jürgen Gluch<sup>2</sup>, Matthias Kraatz<sup>2</sup>, André Clausner<sup>2</sup>, Ehrenfried Zschech<sup>1</sup>

<sup>1</sup>deepXscan GmbH, Zeppelinstr., 01324 Dresden, Germany <sup>2</sup>Fraunhofer Institute for Ceramic Technologies and Systems IKTS, Maria-Reiche-Str. 2, 01109 Dresden, Germany

\*kristina.kutukova@deepxscan.com

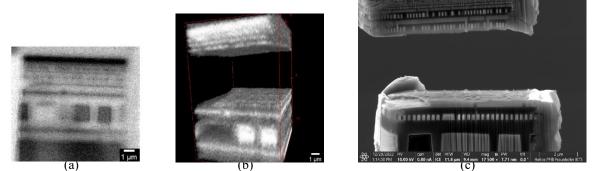

Recent developments in transmission X-ray microscopy (TXM) and high-resolution X-ray computer tomography (nano-XCT) make in-situ studies of microcrack evolution in 3D nanopatterned systems, e,g, in fully integrated backend-of-line (BEoL) interconnect stacks of ICs, possible [1]. Merging high-resolution nondestructive 3D imaging and a miniaturized micromechanical test allow to study the fracture behavior of Cu/low-k stacks and to determine local mechanical properties of materials at the micro- and nanoscale.

In this study, two miniaturized piezo-driven double cantilever beam (micro-DCB) test set-ups were applied in a laboratory TXM (photon energy 8 keV) to study in-situ microcrack opening and propagation in the Cu/low-k BEoL stack of a microchip manufactured in 14 nm CMOS technology node [2]. For both micromechanical testers, image analysis procedures were developed and applied, and the local energy release rate G at the crack tip was determined for sub-100nm regions, by extending the classical fracture mechanics to small dimensions.

During the micro-DCB test at the miniaturized sandwich-like sample, the geometry of the microcrack was imaged with about 100 nm resolution at several loading steps. The subsequent data analysis - applying linear elastic fracture mechanics and the Euler-Bernoulli beam model - allowed to determine the critical energy release rate  $G_c$  for crack propagation in sub-100 nm regions of a BEoL stack quantitatively. Particularly,  $G_c$  was experimentally determined at the crack tip for different regions of the wafer: in the scribe line (SR), near the metallic guard ring (GR) structure and in the patterned Cu/low-k interconnect stack. It was shown that the GR structures significantly increase the critical energy release rate  $G_c$  for crack propagation compared to the values in patterned surrounding regions, and it is about one order of magnitude higher than the  $G_c$  values measured for the respective unpatterned dielectric thin films.

The determination of local mechanical properties of materials as described in this study allows to evaluate process-induced materials changes and it provides a pathway to study the scaling of mechanical properties of interconnect stack materials of advanced ICs. The experimental results gathered at realistic interconnect structures provide valuable information to control the fracture path in the BEoL stacks and for the design of guard ring structures to ensure the requested mechanical robustness of advanced ICs.

#### Acknowledgments

The authors thank Han Li, Intel Inc, Hillsboro/OR, USA, for valuable discussions. Financial support from SRC under Member-Specific Research Contract P30697 is greatly appreciated.

#### References

[1] K. Kutukova et al., Appl. Phys. Lett. 2018, 113, 091901.

[2] K. Kutukova et al., Materials & Design 2022, 221, 110946.

## Indentation-induced delamination and adhesion work evaluation at elevated temperature in industrial semiconductors

Pal-Jen Wei<sup>1</sup>\*

### <sup>1</sup>Bruker, 3F-3, No. 6, Taiyuan 1st street, Zhubei City, Hsinchu 30288 Taiwan

#### \*Pal-Jen.Wei@bruker.com

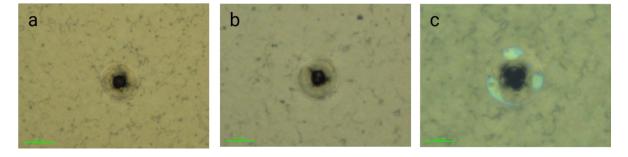

Film adhesion is critical to the performance of semiconductor devices, with interfacial delamination and fracture nearly always leading to device failure. Here, indentation tests were applied to thin film devices in order to induce stresses to cause delamination. A discontinuity in the load-displacement behavior "pop-in" indicates a critical stress to cause interfacial delamination. The loads at these pop-in events are found to have a proportional relationship with the critical load results of the more common scratch test, providing a basis for converting critical forces from the two methods. Nanoindentation, combined with a variable temperature stage that provides a stable and uniform micro-environmental chamber, allows for the probing of critical forces throughout the temperature range of expected device operation.

The delaminated region that occurs after the unloading of the indentation results in a region that bulges from the original surface, as the film is suspended over the substrate. This region can be measured using SPM or optical imaging of the region, and a radius of delamination, r, and the contact radius, a, can be obtained. This information, combined with the film hardness, H, and modulus, E, determined from standard nanoindentation tests at forces lower than result in delamination, allow the calculation of the strain energy release rate, G, through the following equation.

#### [1].

**Figure 1.** Optical images of indentation-induced delamination of polyimide/copper interface for determination of contact radius and delaminated radius at (a) 35°C; (b) 150°C; (c) 215°C.

#### References

[1] L.G. Rosenfeld, et al., Journal of Applied Physics 1990, 67(7), 3291.

## Piezoresistive Characteristics of MOSFET Channels Determined with Indentation Stress-induced Ring Oscillator Parameter Shifts

André Clausner<sup>1</sup>\*, Simon Schlipf<sup>2</sup>, Jens Paul<sup>2</sup>, Simone Capecchi<sup>2</sup>, Christoph Sander<sup>1</sup>, and Ehrenfried Zschech<sup>3</sup>

<sup>1</sup> Fraunhofer IKTS, Maria-Reiche-Str. 2, 01109 Dresden, Germany <sup>2</sup> GLOBALFOUNDRIES Dresden, Germany <sup>3</sup> deepXscan Dresden, Germany

#### \*andre.clausner@ikts.fraunhofer.de

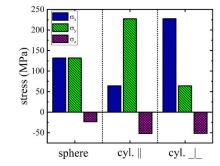

The mechanical stress/strain-related changes in the characteristics of transistors manufactured in the 22 nm node of the fully depleted silicon on insulator (FDSOI) CMOS technology is studied with advanced experimental indentation designs. Precisely, NAND and NOR ring oscillator circuits are used to monitor the strain-caused charged carriers mobility changes in the silicon transistor channels. Piezoresistive coefficients for strained silicon are then calculated from the experimental indentation data using spherical [1] and cylindrical [2] tip geometries as well as for comparison four-point bend (4PB) experiments [3]. In contrast to spherical tips, cylindrical indentation tips as well as 4PB experiments enable to induce the mechanical stresses and strains more selectively into a specific spatial direction. To set up the experimental details appropriately, numerical Finite Element Method (FEM) simulations of the experimental designs have been used. Additionally, FEM studies are conducted to compute the quantitative stress and strain values in the silicon transistor channels as a function of contact load as well as chip and tip geometries, see Fig. 1. Using the signal deviations of the RO circuits subjected to these quantitative strain and stress data from spherical and cylindrical indentation (derived by FEM), a set of equations using the linearized piezoresistive model are created to determine the directional piezoresistive coefficients [4].

Figure 1. FEM computed normal stress tensor components in the ring oscillator structures for spherical and cylindrical indentation experiments.

#### Acknowledgments

The presented work has been created within the IPCEI projects RingO and RingO2 conducted in close collaboration with GLOABALFOUNDRIES Dresden and the excellent PhD work of Simon Schlipf.

#### References

- [1] Schlipf et al., J. Vac. Sci. Technol. B 2020, 38, 063206.

- [2] Schlipf et al., *IEEE Transactions on device and materials reliability* **2022**, VOL. 22, NO. 3.

- [3] Schlipf et al., Transactions of 22nd International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE) **2021**.

- [4] Schlipf et al., IEEE Transactions on Electron Devices 2021, vol. 68, no. 4.

## Hybrid Dielectric Films for Device Technologies: Understanding Relationships between Molecular Structure, Processing and Function

Reinhold H. Dauskardt\*, Karsu I. Kilic

#### <sup>1</sup> Department of Materials Science and Engineering Stanford University, Stanford, CA 94305

#### \*dauskardt@stanford.edu

Emerging interconnect technologies with increased performance of microchips necessitate the reliable integration of ultra-low-k dielectric materials such as hybrid organosilicate glasses (OSG) as insulating units to prevent crosstalk. However, the process of obtaining nanoscale trench patterns densely filled with low-k dielectrics between conducting units has been challenging as the feature sizes become smaller. One of the main challenges is the undesired formation of low density regions in the low-k dielectric material filled inside the gap which complicates the proper scalability of low-k dielectric materials, as well as leading to poor device reliability.

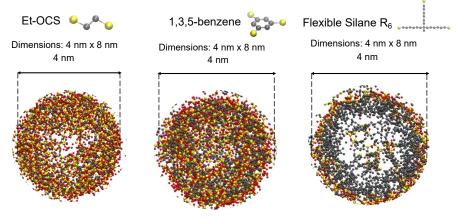

Using molecular dynamics simulations, we work to develop computational modeling strategies where we explore the way different hybrid OSG precursors pack under nanoscale confinement and interact with the trench material to understand the role of precursor structure and OSG-trench interaction on the formation of low density. This will ultimately guide experimental efforts in terms of precursor selection to achieve controlled density to enhance mechanical reliability. Our simulation results show that *hyperconnected* and *cyclic* 1,3,5-benzene precursor molecules pack more homogeneously under nanoscale confinement compared to precursors such as conventionally connected Et-OCS (ethylene bridged) molecules (Fig. 1). We demonstrate that the more homogenous distribution and better crosslinking abilities of hyperconnected 1,3,5-benzene precursors under confinement together lead to the formation of more uniform filling and better connectivity of the hybrid material formed inside the feature; thereby yielding improved elastic and fracture properties compared to the hybrid OSG derived from precursors such as the Et-OCS molecule.

**Fig. 1:** Molecular morphology of low-k dielectric organosilicate fillings derived from Tt-OCS, 1,3,5-benzene and flexible silane precursors. The gap aspect ratio was 1:2 and the gap depth 4 nm. 1,3,5-benzene molecules result in more uniform density compared to Et-OCS and flexible silane molecules.

#### Acknowledgments

The work was supported in part by the Semiconductor Research Corporation (SRC).

## Solid-phase bonding process using nanostructured surface for power devices in automotive

Hiroshi Nishikawa<sup>1</sup>\*

<sup>1</sup>Joining and Welding Research Institute, Osaka University, 11-1 Mihogaoka, Ibaraki, 567-0047 Osaka, Japan

#### \*nisikawa@jwri.osaka-u.ac.jp

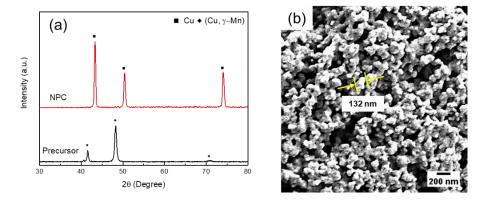

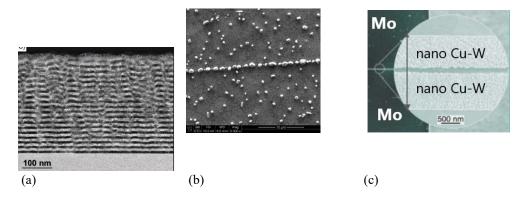

Wide bandgap (WBG) semiconductors, such as SiC and GaN, are being developed as promising replacements for Si-based semiconductors because they have high power density, operation frequency, and break down voltage. These WBG semiconductors can operate efficiently at temperatures above 300 °C. Compared with the conventional silicon (Si) device, the SiC device can operate with significant lower power loss and higher operating temperature, which contributes to miniaturization and higher performance of power modules. To assemble these devices, the high-temperature bonding process as a die bonding process is one of the key technologies. Then, the EU RoHS directive currently exempts the use of high-lead-containing solders such as Pb-5Sn and Pb-10Sn solders in electronic packaging. However, there is no guarantee that the exemption will last. A strong drive thus exists to find lead-free alternatives for the SiC power devices. Recently, sintering metallic nanoparticles such as Ag and Cu have been explored by virtue of their high melting temperatures and superior electrical and thermal conductivities [1, 2]. However, the nanoparticle paste contains various organic substances. During the bonding process, residual organic materials can induce the formation of unexpectedly large voids or gaps in the joint layer. The nanoparticle paste has some problems for practical use. To avoid the problems, we have proposed a solid-state bonding process without solvents using a metal sheet with nanostructured surface [3]. In this talk, I will introduce new approach on die bonding materials and processes using the metal sheet with nanostructured surface. I will introduce a manufacturing process of nanoporous sheets in dealloying [4] and a pressure-assisted nanoporous bonding (NPB) for die bonding process. Basic experimental test results such as joint strength and interfacial behavior with a substrate will be also explained. For example, nanoporous Cu (NPC) sheets were fabricated from Mn-Cu precursor sheets with thicknesses of 110-120 µm. The NPC sheet was prepared using the dealloying method, which involved the selective dissolution of Mn into 4 % hydrochloric acid from the Mn-Cu precursor. XRD patterns of the precursor sheet and the as-dealloyed NPC sheet are shown in Fig. 1(a). Furthermore, the surface morphology of the NPC sheet (ligament size = 132 nm) fabricated by dealloying a precursor sheet is illustrated in Fig. 1(b).

Figure 1. (a) XRD patterns of the precursor sheet and as-dealloyed NPC sheet. (b) SEM images of the structure of the as-dealloyed NPC sheet.

#### References

- [1] E. Ide et al., Acta Materialia 2005, 53, 2385.

- [2] H. Nishikawa et al., The Open Surface Science Journal 2011, 3, 60.

- [3] M. S. Kim et al., Mater. Sci. Eng. A 2015, 645, 264.

- [4] J. Erlebacher et al., Nature 2001, 410, 450.

## Hybrid bond and nanowired bump technologies for high density interconnect formation on wafer level

Iuliana Panchenko<sup>1,2,\*</sup>, Laura Wenzel<sup>1,2</sup>, Steffen Bickel<sup>1,2</sup>, Adil Shehzad<sup>1</sup>, Maik Mueller<sup>2</sup>, Catharina Rudolph<sup>1</sup>, Sebastian Quednau<sup>3</sup>, Olav Birlem<sup>3</sup>, Andreas Graff<sup>4</sup>, Frank Altmann<sup>4</sup>, Manuela Junghähnel<sup>1</sup>

<sup>1</sup> Fraunhofer IZM ASSID, Ringstr. 14, Moritzburg, <sup>2</sup>Institute of Electronic Packaging Technology, TU Dresden, Helmholtzstr. 10, Dresden, <sup>3</sup> NanoWired GmbH, Emanuel-Merck-Str. 99, Gernsheim, <sup>4</sup> Fraunhofer IMWS, Walter-Hülse-Str. 1, Halle

\*iuliana.panchenko@assid.izm.fraunhofer.de

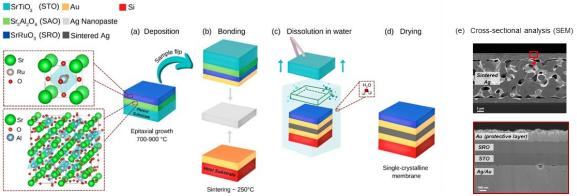

This study starts with an overview of different fine-pitch interconnect technologies, which are based on solder (Cu pillar with solder cap, solid-liquid interdiffusion bonding) and pure Cu metal (Cu/Cu thermo-compression and ultrasonic bonding, Cu/SiO<sub>2</sub> hybrid bonding, nanowired bump). Those technologies are required for the packages with high I/O number and especial for heterogeneous 2.5D or 3D chiplet integration. The application fields are consumer electronics, high-performance computing, artificial intelligence, etc. The advantages and disadvantages of these interconnect technologies as well as process flows will be addressed. The recent demand in chiplet integration is a combination of at least two different interconnect technologies for the bonding on one interposer, which requires changes in a current process flow.

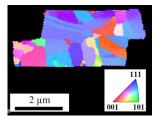

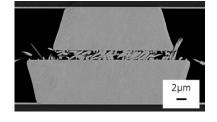

The result chapter of this study is an overview of two Cu interconnect technologies for wafer level based on hybrid bond pads and nanowired bumps. Both are excellent candidates for small interconnect diameters between 3 µm and 25 µm. Nanowires used for the bumping process were 100 nm and 200 nm in diameter. Hybrid bond processing requires a demanding chemical-mechanical planarization, particle-free dicing technology (in case of die-to-wafer bonding) and surface activation. We report on bonding results both for wafer-to-wafer and die-to-wafer, as well as detailed microstructure (grain orientation analysis by Electron-Backscatter-Diffraction, EBSD) characterization of the bonded interconnects (Fig. 1a) [1]. The nanowired bump processing has several simplifications against the hybrid bond pad preparation, however it needs an alternative process for the removal of the Cu seed layer. We report on the proposed process flow and die-to-die bonding results [2], as well as microstructure of the nanowired bumps (Fig. 1b). We also address the high-resolution TEM results of the Cu nanowired interconnects.

a) Hybrid bond interconnect (ø4µm top pad) – EBSD map

b) Nanowired Interconnect (ø25µm top bump) – SEM image

Fig. 1 Exemplary images of the microstructure of the hybrid bond interconnect (a) and nanowired interconnect (b)

#### Acknowledgments

This study is an overview of two comprehensive wafer level interconnect technologies at fine scale, therefore we acknowledge the whole staff of Fraunhofer IZM ASSID involved in the wafer processing. Financial support for this study was provided over following projects: "Functional Integration for Micro-/Nano-Electronics" under Grant 100245395 and Grant 100249378 and "Transfer center: Functional Integration for the Micro-/Nano-Electronics" under Grant 100368159 and Grant 100368161, "Wafer Metrology Center" EU project 16ME0057, "NanoInt" Fraunhofer SME internal project.

#### References

- [1] I. Panchenko et al., *IEEE Transactions on Components, Packaging and Manufacturing Technology*, **2022**, vol. 12, no. 3.

- [2] A. Shehzad et al., Proceedings of the ESTC conference, 2022, pp. 118-123.

## Phase change materials for embedded memories: *in situ* investigation of crystallization behavior using synchrotron radiation

Olivier Thomas<sup>1</sup>\*, Philipp Hans<sup>1</sup>, Cristian Mocuta<sup>2</sup>, Christophe Guichet<sup>1</sup>, Y. Le-Friec<sup>3</sup>, P. Boivin<sup>4</sup>, R. Simola<sup>4</sup>, P. Noé<sup>5</sup>, S. Jeannot<sup>3</sup>

<sup>1</sup> Aix Marseille Univ, Univ Toulon, CNRS, IM2NP UMR 7334, Marseille, France

<sup>2</sup> Synchrotron SOLEIL, L'Orme des Merisiers, Saint-Aubin - BP 48, 91192 Gif-sur-Yvette Cedex, France

<sup>3</sup> STMicroelectronics, 850 rue Jean Monnet, 38920 Crolles, France

<sup>4</sup> STMicroelectronics, 190 Ave Coq, 13106 Rousset, France

<sup>5</sup> Université Grenoble Alpes, CEA-LETI, MINATEC, 17 rue des Martyrs, 38054 Grenoble, France

\*olivier.thomas@univ-amu.fr

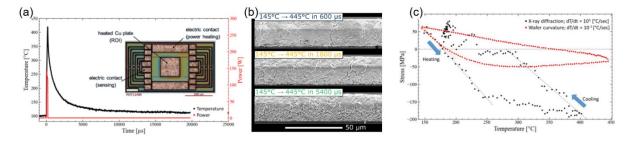

Phase Change Memory is a very promising non-volatile memory that is being considered by several companies for a wide range of applications (storage-class memory, in-memory computing, neuromorphic computing, eNVM for microcontrollers ...). Among Phase Change Materials (PCMs) the ternary Ge-Sb-Te phase diagram offers a rich variety of interesting phases including the much-studied compounds  $Ge_2Sb_2Te_5$  and GeTe. At STMicroelectronics a new Ge-rich Ge-Sb-Te alloy (GGST) has been developed with a crystallization temperature above  $350^{\circ}C$  [1] for addressing the specific needs of the automotive market where high operating temperatures are required.

During the last years we have investigated the crystallization and mechanical behavior of these PCMs using X-ray diffraction as a function of temperature during annealing. Capped thin films are heated *in situ* under nitrogen atmosphere [2,3,5] on the DiffAbs beamline of SOLEIL synchrotron facility. The incident beam is monochromatic (18 keV) and the incidence is fixed. A bidimensional detector collects the diffraction pattern and is corrected and integrated [4] to yield a 1D diffraction pattern. The diffraction peaks are then fitted with an analytical function that allows extracting the integrated intensity, integral breadth and position of the Bragg peaks. These parameters allow following the crystallization kinetics and the thermomechanical behavior [2,3] of thin films as a function of various parameters: doping, film thickness (5 nm – 50 nm), nature of surrounding layers ... In addition, we will show that, thanks to the high flux and penetrating power of synchrotron X-rays, patterned and metallized structures close to real products can be investigated. The results obtained from such *in situ* investigations bear important consequences for the understanding of the crystallization process in memory cells.

#### Acknowledgments

The authors gratefully acknowledge the SOLEIL Synchrotron for allocating beam time. P. Joly, is acknowledged for excellent technical support during the experimental campaigns at SOLEIL Synchrotron on DiffAbs beamline. This research was supported partly by IPCEI/Nano 2022 program and by ANR under contract SESAME ANR-15-CE24-0021.

#### References

[1] P. Zuliani et al., Solid State Electronics 2015, 111, 27.

- [2] M. Gallard et al., Acta Materialia 2020, 191, 60.

- [3] O. Thomas et al., *Microelectronic Engineering* **2021**, *244*, 11573.

[4] C. Mocuta et al., Journal of Applied Crystallography 2014, 47, 482.

[5] P. Hans et al., Physica Status Solidi RRL 2022, 2100658.

## Controlled microcrack steering into toughened regions – What microelectronics can learn from nature?

Ehrenfried Zschech<sup>1</sup>\*, Martyna Strag<sup>2</sup>, Kristina Kutukova<sup>1</sup>

<sup>1</sup>deepXscan GmbH, Zeppelinstr. 1, 01324 Dresden, Germany <sup>2</sup>Military Institute of Armament Technology, Prymasa Stefana Wyszyńskiego 7, 05-220 Zielonka, Poland

#### \*ehrenfried.zschech@deepxscan.com

The advent of evolutionary developmental biology in the final decades of the 20<sup>th</sup> century was based on the fact that biologists – together with architects and engineers – established a theoretical basis for the science of form. Modern morphological research (see e.g. [1]) has not only impact on biology but also on architecture and materials science. It provides a new interdisciplinary perspective to the design of materials. The transfer of biological principles into architecture and material design has a huge potential in solving technical problems by natural forms. In particular, the goal of biomimetics is to implement a biologically informed material system that relies equally on construction principles in nature and those in fabrication [2].

A proven "damage-tolerant design" of nature are biocomposites that contain components with high fracture toughness. As an example, high-resolution X-ray imaging of the outermost layer of a mollusk shell shows that the propagation of microcracks that have been initiated by an indent are steered into and finally trapped in an amorphous organic phase with high fracture toughness, located between calcite building blocks [3]. Studies at biological objects, combining experimental data and modeling, can help to develop fracture mechanics at small scales and to understand microcrack propagation in hierarchically structured material systems.

Learning from nature, an approach for avoiding mechanical damage of microchips manufactured in leadingedge CMOS technology nodes is a controlled steering of microcracks, e.g. generated during the wafer dicing process, into regions with relatively high fracture toughness [4]. One option to prevent material cracking and interface delamination in BEoL stacks is the integration of metallic guard ring (GR) structures at the rim of the microchip. These specially designed metal structures are integrated into BEoL stacks to dissipate energy in such a way that crack propagation is efficiently slowed down and eventually stopped. Experimentally, a displacement-controlled crack propagation through the Cu/low-k stack and a controlled crack steering were realized in a miniaturized piezo-driven double-cantilever beam (DCB) test, by a combination of loading modes, i.e. a tuned fracture mode mixity locally at the crack tip. This mechanical test set-up was positioned in the beam path of a laboratory transmission X-ray microscope (TXM) for imaging the pathways of microcracks with sub-100nm resolution in the region of interest (ROI) that includes the BEoL and particularly the GR structures [5]. With the methodology described, i.e. the controlled steering of microcracks into regions with high fracture toughness while considering nanoscale mechanical properties of fully integrated 3D interconnect stacks (particularly the local critical energy release rate G<sub>c</sub>), conclusions for the robustness of BEoL stacks can be drawn and input for the design of GR structures can be provided [6].

#### References

[1] M. Tamborini, "The Architecture of Evolution, The Science of Form in Twentieth-Century Evolutionary Biology", University of Pittsburgh Press (2022)

[2] A. Menges, T. Schwinn, "Manufacturing reciprocities", Architectural Design 82 (2), 118 – 125 (2012)

[3] <u>M. Strag, Ł. Maj, M. Bieda, P. Petrzak, A. Jarzębska, J. Gluch, E. Topal, K. Kutukova, A. Clausner, W. Heyn, K. Berent, K. Nalepka, E. Zschech, A. G. Checa, K. Sztwiertnia, "Anisotropy of Mechanical Properties of Pinctada Margaritifera Mollusk Shell", Nanomaterials 10(4) 634 (2020)</u>

[4] E. Zschech, M. R. Elizalde, "Mechanical Robustness of Patterned Structures and Failure Mechanisms", in "More-than-Moore Devices and Integration for Semiconductors", (Eds. F. Iacopi, F. Balestra), Springer, Cham, pp. 157 – 189 (2023)

[5] K. Kutukova, S. Niese, J. Gelb, R. Dauskardt, E. Zschech, "A Novel Micro-Double Cantilever Beam (micro-DCB) Test in an X-ray Microscope to Study Crack Propagation in Materials and Structures", Mater. Today Comm. 16, 293–299 (2018)

[6] K. Kutukova, J. Gluch, M. Kraatz, A. Clausner, E. Zschech, <u>"In-situ X-ray tomographic imaging and controlled steering of microcracks in 3D nanopatterned structures</u>", Materials & Design 221, 110946 (2022)

# Degradation mechanisms of 10kV-reinforced isolated gate drivers at high switching frequencies greater than 30kHz

Matthias Stecher<sup>1)\*</sup>, Leonard A. Dissado<sup>2)</sup>

<sup>1)</sup>Infineon Technologies, 85579 Neubiberg, Germany <sup>2)</sup> Prof. Emeritus, Dep. of Eng., Uni. of Leicester, Uni. Road, Leicester, LE1 7RH, U.K

#### \*Matthias.Stecher@infineon.com

Galvanic isolated couplers are commonly used in industrial, telecom and automotive systems to counteract ground potential differences and to protect the user against high voltage shock. Hence, the robustness of the galvanic insulation of couplers has to be guaranteed over the operating life of the equipment. The design of such equipment is a challenging task because, for example, even an AC/DC power converter for a home appliance (e.g. a laptop computer) has to withstand not only the 220V system voltage, but also the PWM (pulse width modulation) recurring peak voltages reaching several hundred volts, overvoltage occurrences due to power grid instability and surge pulses (1.2µs rise-time and 50µs fall-time) generated due to lightning outside the home. These power grid disturbances can reach several thousand volts at the 220V-AC side of the power converter. To guarantee the robustness of such appliances they must be certified by independent test houses such as the VDE, TUEV or UL. The certification is performed on the basis of several standards, such as the IEC 60664 (Insulation coordination for equipment within low-voltage systems), IEC 62368 (Safety requirements for audio/video, information and communication technology equipment) and IEC 60747-17 (safety requirements for magnetic/capacitance couplers). According to these standards, all PWM applications running below 30kHz can be certified via voltage tests at 50Hz. Above 30kHz the dielectric insulation thickness has to be increased by a factor of two at minimum.

The typical IC coupler design solution consists of two chips, one for the primary and the other one for the secondary side [1]. Each chip is placed on its own lead-frame paddle within a molded IC package. A high-voltage capable transformer or capacitance is placed on one or both of these two chips to provide a signal path between the primary and secondary sides. The connection between the chips is done by bond-wires via the top winding/electrode of the transformer/capacitance. The dielectric material and the thickness between the paddles and within the transformer/capacitance must be chosen to withstand several thousand volts. The typical SiO2 isolation thickness in the transformer/capacitance is between 10 and  $30\mu m$  for PWM applications running below 30kHz. There is also a parasitic E-field above the transformer/capacitance which stresses the mold compound above the chip passivation. This can reach several  $100V/\mu m$ .

To increase the power efficiency, the PWM switching frequency has been increased from 30kHz up to several hundred kHz in recent years, thanks to the introduction of GaN and SiC power transistors. The abovementioned standards already require for a 100kHz PWM application a 2-4 times thicker isolation than that for an 30kHz application. Whether this required thickness increase is justifiable has been analyzed based on material test structures stressed using high voltages (3-10kV) and high frequency (30, 150, 450, 800kHz) for very long periods of time. The results indicate that the life-time of the coupler at high voltages is determined by the SiO2 within the transformer/capacitance while at medium voltages the determining factor is the mold-compound on top of the chip. The experiments furthermore show that the life-time actually increases with increasing frequency, suggesting therefore that a thicker isolation than the one used for a 30kHz application is not needed. For both the SiO2 and the mold compound a threshold E-field can be determined, below which the main degradation mechanism is not even visible. This presentation will provide details of the experiments, results and possible degradation models.

#### References

J. Paye et al, "High Voltage Robustness of Mold Compounds under Different Environmental Conditions", 2015 IEEE International Reliability Physics Symposium

## Contrasting Stress Evolution During Lithiation and Delithiation of Different Electrode Materials for Thin Film Batteries

Carl V. Thompson<sup>1</sup>\*, Lin Xu<sup>1</sup>, Michael J. Chon<sup>1</sup>

### <sup>1</sup>Department of Materials Science and Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139, USA

#### \*cthomp@mit.edu

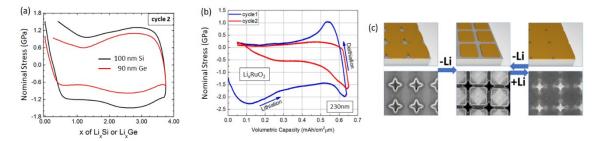

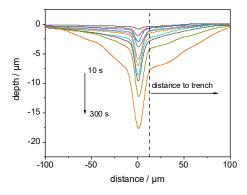

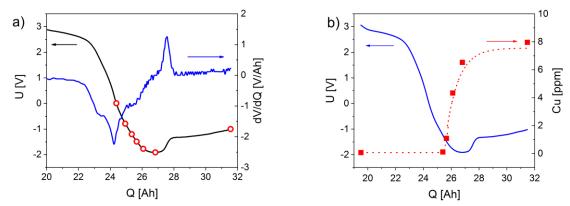

Thin film Li-ion batteries with high energy capacity and cyclability are needed for autonomous microsystems such as sensors used for a wide range of applications in the Internet of Things. Silicon and germanium can serve as high capacity anodes, and for applications in microsystems,  $RuO_2$  can serve as a high capacity cathode. The high Li capacity of these materials causes volume expansions of 250-300% that can lead to mechanical failure and poor cyclability. In-situ measurements show that compressive and tensile stresses of order 1 GPa develop in Si and Ge (Fig. 1(a), [1]). However, the behavior of  $RuO_2$  is fundamentally different, with low tensile stresses during the 2<sup>nd</sup> and subsequent delithiation cycles and a more gradual increase in the compressive stress during lithiation (Fig. 1(b), [2]). Using lithographically patterned arrays of notched holes in  $RuO_2$  films, this behavior was shown to be associated with reversible sliding at the interface between  $RuO_2$  and the underlying current collector (Fig. 3(c), [3]). Regular arrays of channel cracks formed at locations controlled by the notched holes, leading to formation of square islands of  $RuO_2$  film. In subsequent cycling, these wide channel cracks reversibly closed and opened during lithiation.

**Figure 1:** a) Nominal stress measured in situ during lithiation/delithiation cycles of (a) Si and Ge films and (b) a RuO<sub>2</sub> film. (c) RuO<sub>2</sub> films patterned with an array of notched holes. Channel cracks form to create square islands of RuO<sub>2</sub>. Subsequent cycling causes the channel cracks to reversibly close and open.

#### Acknowledgments

This research was supported by the National Research Foundation, through the Singapore-MIT Alliance for Research and Technology (SMART).

#### References

[1] A. Al-Obeidi, D. Kramer, C.V. Thompson, and R. Mönig, J. Power Sources 2015, v297, p472.

[2] L. Xu, M. J. Chon, B. Mills, and C. V. Thompson, J. Power Sources 2022, v552, p232260.

[3] L. Xu and C. V. Thompson, ACS Appl. Nano Mater. 2021, v4, p1370

## Tortuosity and Porosity in Electrochemical Systems - Computed Tomography Based 3D Transport Modelling

Robert Filipek<sup>1</sup>\*, Ehrenfried Zschech<sup>2</sup>

<sup>1</sup>AGH University of Science and Technology, Faculty of Materials Science and Ceramics, al. Mickiewicza 30, 30-059 Kraków, Poland. <sup>2</sup>deepXscan GmbH, Zeppelinstr. 1, 01324 Dresden, Germany.

#### \*rof@agh.edu.pl

Even up-to-date advanced studies of the transport and reactions in electrochemistry are characterized either by essentially homogeneous treatment of the system (with possible including several species, ions and neutral molecules) with non-linear electrode kinetics (Butler-Volmer or Tafel equations) or by a more sophisticated treatment of the system (including its real micro-structures), but with a simple transport model (one species only and simple Fickian diffusion).

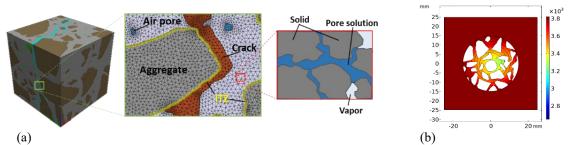

Two examples will illustrate a new more general attempt for the description of transport and reactions in electrochemical systems. The first example concerns the influence of ions activities and materials structure on ions transport, a problem of a fundamental importance for safety of reinforced concrete structures, in particular for understanding and minimizing corrosion of rebars in concrete. The second example demonstrates the influence of the material's porosity and its 3D microstructure on the infiltration of the material. The Navier–Stokes and mass balance equations are solved in the continuous porous structure and the results are compared with simplified simulations which assume a homogeneous material and with average properties (porosity, tortuosity and constrictivity) accounting for its complex morphology.

Figure 1. (a) 3D hierarchical concrete structure; (b) Chloride ion concentration in concrete sample (2D cross-section).

Concluding, the influence of material's nano-/micro-structure on transport in real 3D electrochemical systems and processes is presented. The geometry for the transport is taken from X-ray computed tomography (XCT) measurements. The XCT results are analysed and using specialized algorithms a segmentation of 3D structure is performed which is used for 3D mesh generation. The mesh prepared in this way is then utilised in finite element method simulations using COMSOL Multiphysics software and user defined governing equations.

#### Acknowledgments

This research was funded by the National Science Center, Poland, grant No. 2020/37/B/ST8/02805.

#### References

[1] Krzysztof Szyszkiewicz-Warzecha et al., Materials 2023, 16, 1116.

[2] Robert Filipek, Modelling and inverse methods in materials engineering, *Wydawnictwo Naukowe AKAPIT*, Kraków **2019**.

[2] Jakub Stec et al., Ceramics international 2019, 45, 3483.

## **Reliability and Recycling of Battery Materials**

### Jörg Acker<sup>\*</sup>, Thomas Langner, Tim Sieber and Anja Rietig

## Brandenburg University of Technology Cottbus-Senftenberg, Department of Physical Chemistry, 01968 Senftenberg, Germany

#### \*joerg.acker@b-tu.de

Spent lithium-ion batteries (LIB's) are not only a waste object that requires proper disposal due to the hazards emanating from them, but also serve as a source of raw materials with an enormously important economic value for the future of electromobility and energy storage technology.

Today, the vast majority of end-of-life LIBs are still recycled using the pyrometallurgical process, in which complete LIBs are melted in a smelting furnace and the most valuable components, cobalt and nickel, as well as copper (from the substrate foils of the anodes), are recovered as a metallic melt. To recover lithium from slag, on the other hand, requires the effort of "slag design" to convert the lithium into a stable compound that can be easily separated from the rest of the slag.

The second important recycling route is hydrometallurgical processes. The starting point for this is the socalled black mass, which consists of cathode material, anode graphite, conductive carbon black and binder. To recover the black mass, batteries are disassembled to the level of cell stacks or individual cells, and then mechanically crushed. Multi-stage separation processes yield the black mass, which, depending on the process, contains impurities of aluminum, copper and plastic residues. The black mass is dissolved in acidic reagents and, after complex precipitation and extraction processes, nickel, cobalt and nickel are recovered in the form of pure salts, typically as carbonates.

A new, alternative approach is functional recycling, in which the cathode material is recovered from end-oflife LIB's in such a way that its chemical and physical functionality is preserved. This means designing the process so that the particle shape is maintained, the material is not dissolved, the high oxidation states (+4) are preserved, and side reactions that attack the material or cause changes to the particle surface are suppressed. The goal is to recover the material at such a high quality that it can be used as an admixture to virgin material in the production of new batteries.

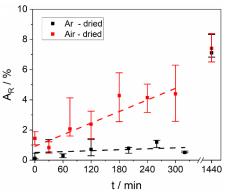

However, functional recycling introduces a variety of challenges that begin with the first step of recycling, the deep discharge of the batteries. Deep discharge means the almost complete transfer of lithium ions from the graphite anode, since lithiated graphite has a similar high chemical reactivity as elemental lithium. The second challenge is the contact of the opened batteries with the ambient air. Here, the volatile components of the electrolyte evaporate, while the low-volatile components and the conducting salt, typically LiPF<sub>6</sub> but also other compounds, remain on the cathode surface. The latter decompose in the presence of atmospheric moisture and initiate a variety of degradation processes on the material.

In the talk, some of the most important aspects and results of functional recycling will be presented, as well as the first industrial process based on this principle. Finally, a brief outlook on the future challenges raised by very nickel-rich cathode materials will be given.

Brandenburgische Technische Universität Cottbus - Senftenberg

## T17

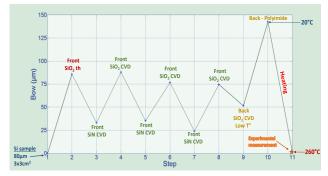

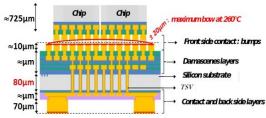

## Strains and stresses control in microelectronic devices: how to optimize the steps from design to manufacturing ?

Lionel Vignoud\* Univ. Grenoble Alpes, CEA Leti, Grenoble, France \*lionel.vignoud@gmail.com