# New reliability challenges for 3D integration stacking using hybrid bonding

Sandrine Lhostis\*1, Bassel Ayoub<sup>124</sup>, Stephane Moreau<sup>2</sup>, Olivier Thomas3, Hélène Frémont<sup>4</sup> \* Member of Technical Staff <sup>1</sup>Department of the Technology for Image Sensors STMicroelectronics

<sup>2</sup>CEA-Leti, Univ. Grenoble Alpes, F-38000 Grenoble, France. <sup>3</sup>Aix-Marseille Université, Université de Toulon, CNRS, IM2NP, Marseille, France.

<sup>4</sup>IMS Laboratory, University of Bordeaux, UMR 5218, 33405 Talence, France

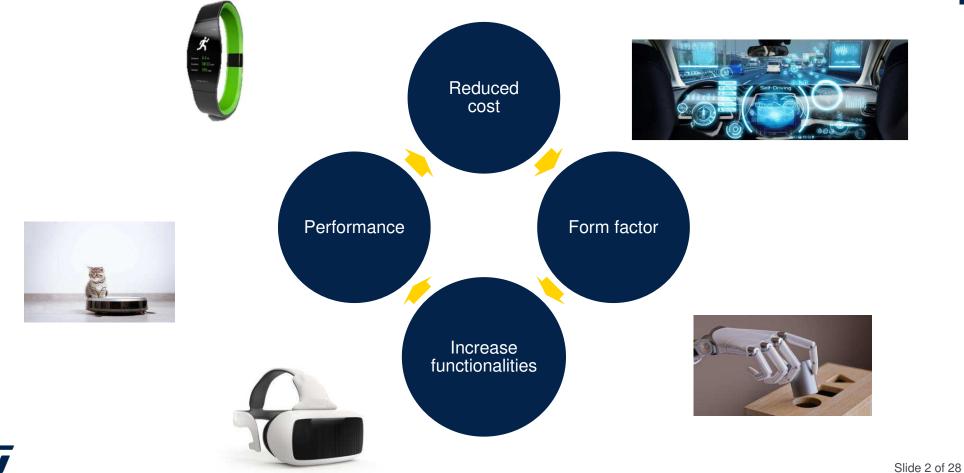

## Driving forces for new devices

life.augmented

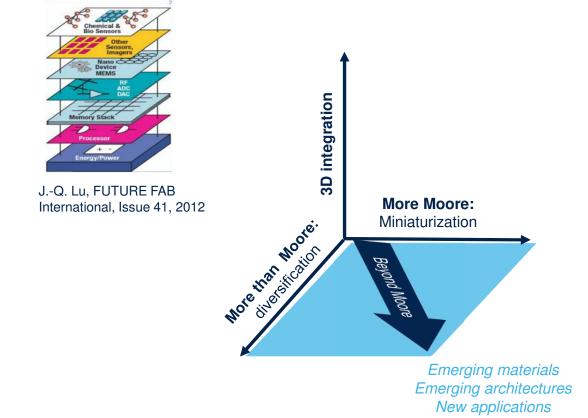

### Going beyond the limits of integration

- **'Beyond Moore:** an approach seeking to achieve the best of both More Moore and More than Moore worlds, and the key to doing so is advanced heterogeneous integration.

- Hybrid bonding stacking being the most scalable 3D integration is a major enabler for More than Moore and will play a determinant role for Beyond CMOS developments

Slide 3 of 28

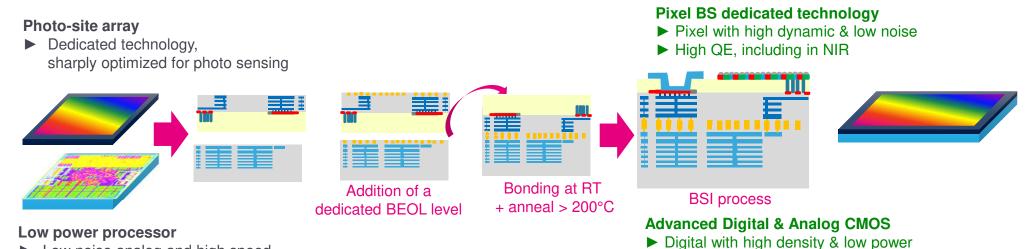

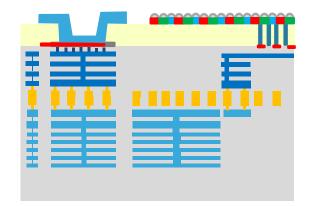

## 3D stacking using hybrid bonding

Massive performant and new functionalities booster for Image Sensor

Low noise analog and high speed, low power, digital imaging

**Dedicated layers introduced to enable hybrid bonding**

Slide 4 of 28

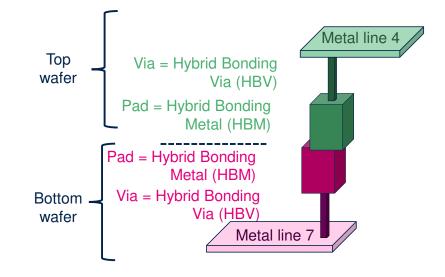

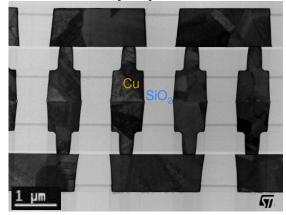

# Hybrid bonding at ST

### Double damascene integration using Cu/SiO<sub>2</sub> materials

1.44 µm pitch

Slide 5 of 28

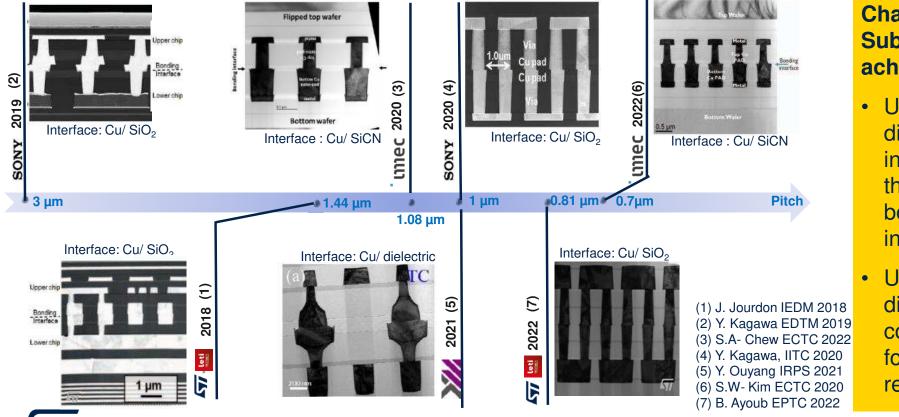

### Capability of high interconnection density

### Main demonstrations over the last 5 years

life.augmented

### Challenging Sub 1µm pitch achievement

- Using different integration at the hybrid bonding interface

- Using different configuration for pad size reduction

Slide 6 of 28

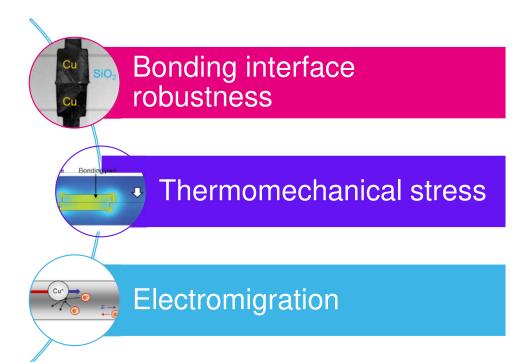

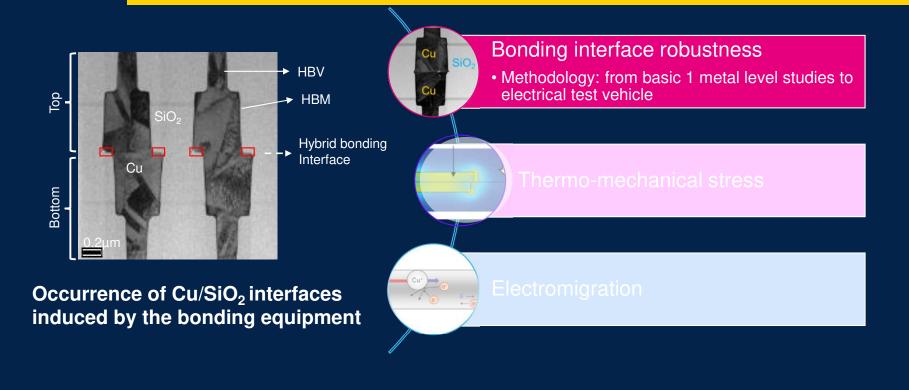

# Reliability challenges using Cu/SiO<sub>2</sub> hybrid bonding?

Could the hybrid bonding levels be considered as new metallization levels with specific weaknesses?

Is there any new concerns with pad width reduction under 1 μm?

Slide 7 of 28

# Cu/SiO<sub>2</sub> stability at the bonding interface

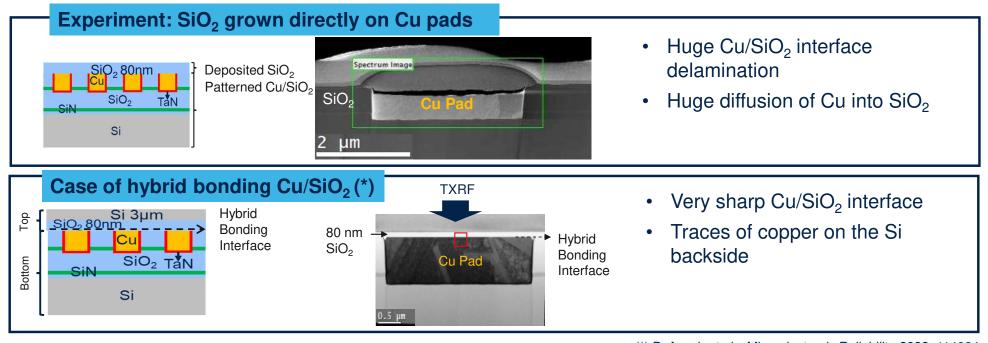

# Thermal stability of the Cu/SiO<sub>2</sub> interface

(\*) B. Ayoub et al., Microelectronic Reliability, 2023, 114934

### No atomic diffusion of Cu through the hybrid bonding interface under thermal stress

Slide 9 of 28

# High Temperature Storage tests

#### No reliability issue under thermal stress whatever the hybrid bonding pad width

Slide 10 of 28

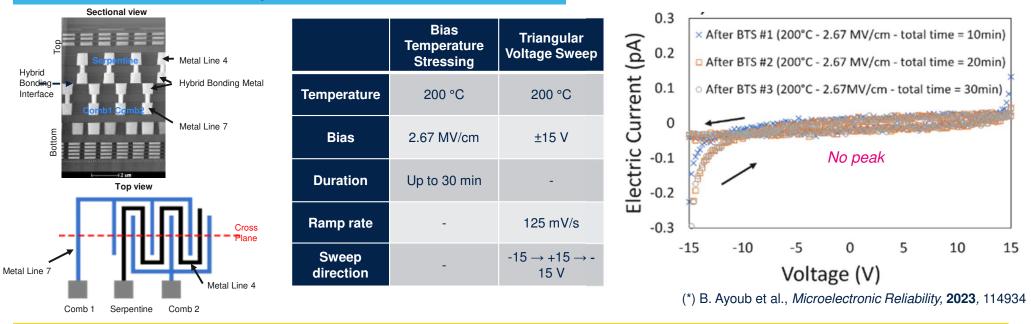

# Study to detect potential ionic diffusion under electrical field

#### BTS/ TVS studies on samples after HTS 4000h (\*)

### No Cu ionic diffusion through the hybrid bonding interface

Slide 11 of 28

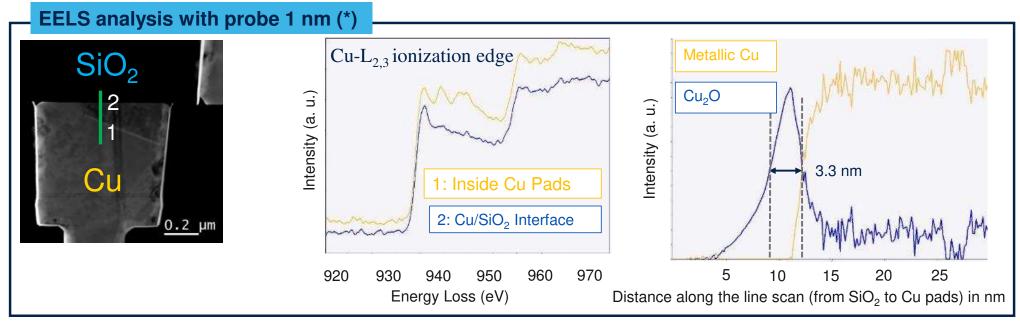

# Composition of Cu/SiO<sub>2</sub> bonding interface

(\*) B. Ayoub et al., *Microelectronic Reliability*, **2023**, 114934.

# Presence of self-formed ~3nm Cu<sub>2</sub>O at the Cu/SiO<sub>2</sub> bonding interface that could act as a diffusion barrier

Slide 12 of 28

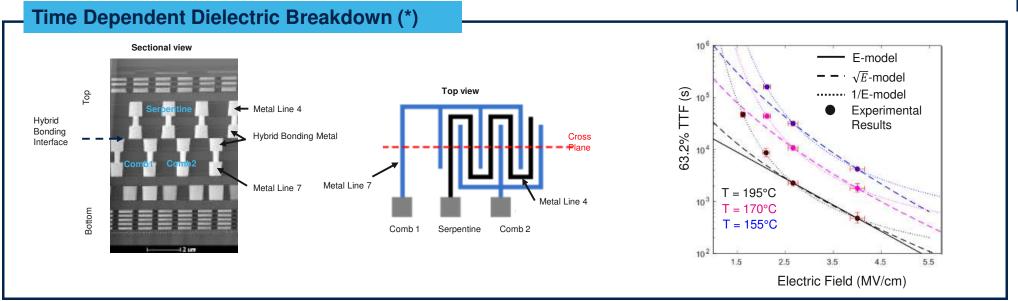

# Impact of any Cu diffusion on dielectric lifetime

(\*) B. Ayoub et al., IEEE International Reliability Physics Symposium (IRPS) 2022

- 1/E model for hybrid bonding while  $\sqrt{E}$  is obtained for other BEoL levels

- Confirms that the role of Cu in TDDB is negligible

### 1/E dependency is attributed to the effective barrier characteristics of the Cu oxide layer

Slide 13 of 28

# Summary on hybrid bonding interface stability

No atomic or ionic Cu diffusion into SiO<sub>2</sub> under thermal stress

No reliability issue under thermal stress

TTF depency to electrical field confirming no Cu assisted breakdown

► A self-formed copper oxide diffusion barrier at the Cu/SiO<sub>2</sub> interface

Slide 14 of 28

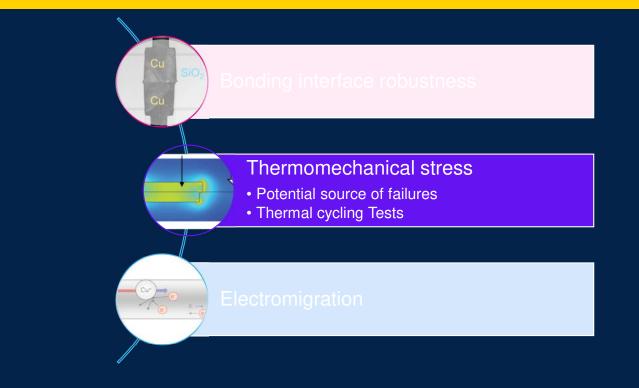

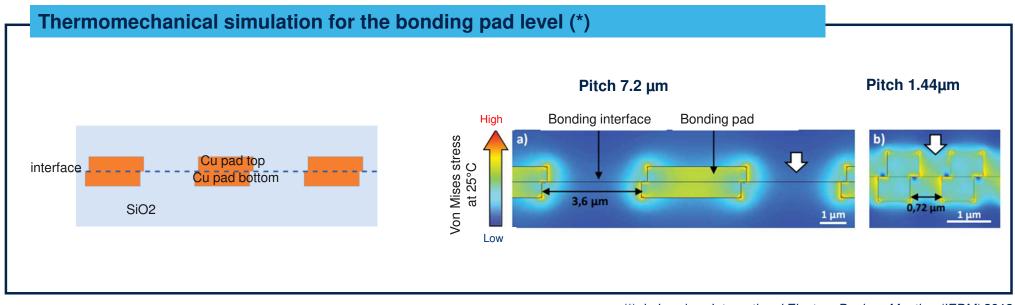

# **Thermomechanical stress**

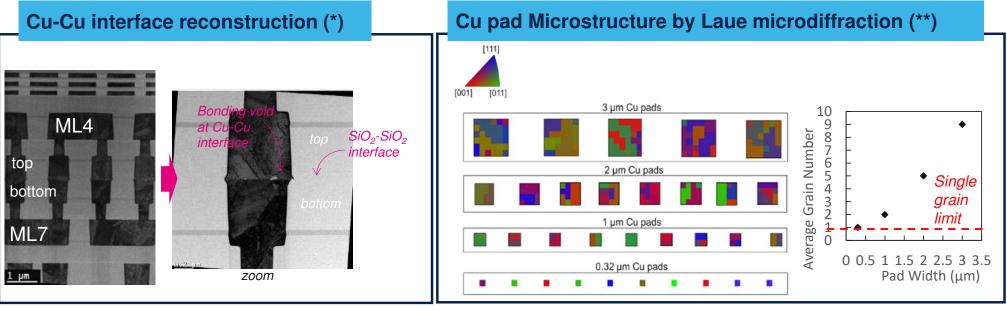

# Interface mechanical stability

(\*) B. Ayoub et al., *IEEE 22nd Electronics Packaging Technology Conference (EPTC)* **2020** (\*\*) B. Ayoub et al., *Microelectronic Engineering* **2022**, *261*, 111809

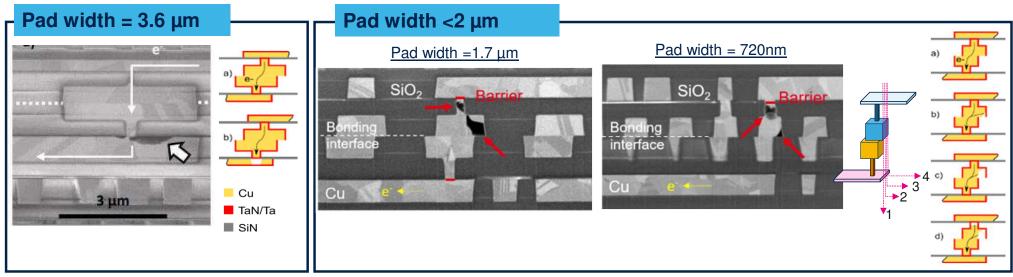

Potential interface delamination under thermomechanical stress with potential different pad reconstruction depending on the pad width

Slide 16 of 28

# Stress at the hybrid bonding level

(\*) J. Jourdon, International Electron Devices Meeting (IEDM) 2018

# Stress at the hybrid bonding level is modified with pad width : potential impact on the robustness to thermomechanical stress

Slide 17 of 28

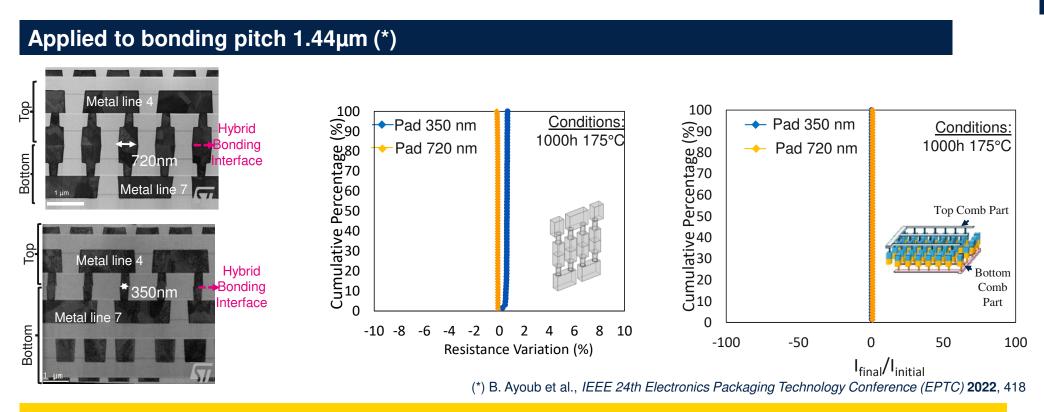

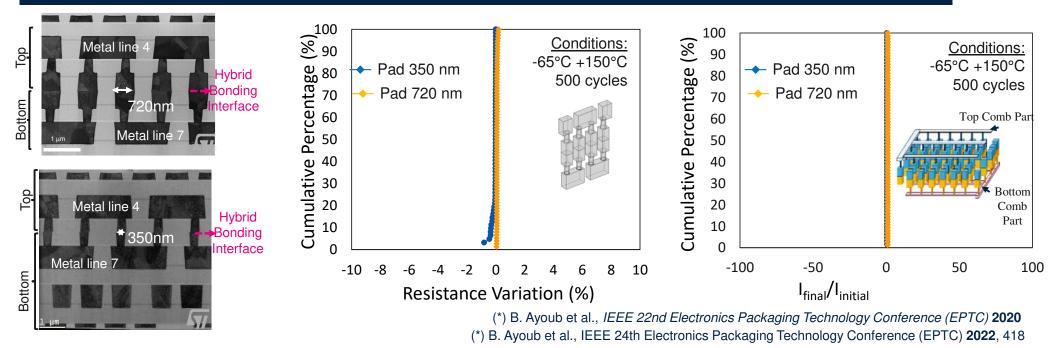

## **Thermal Cycling Tests**

### Applied to bonding pitch 1.44µm (\*)

No impact of hybrid bonding pad width reduction under Thermal Cycling Tests

Slide 18 of 28

# Summary on robustness to thermomechanical stress

The evolution of the Cu pad microstructure with Cu pad size could cause differences on Cu-Cu pad reconstruction

The results of the thermomechanical simulations show higher stress for smaller pitches

► However hybrid Level down to 350nm Cu pad width is reliable towards thermomechanical stress

Slide 19 of 28

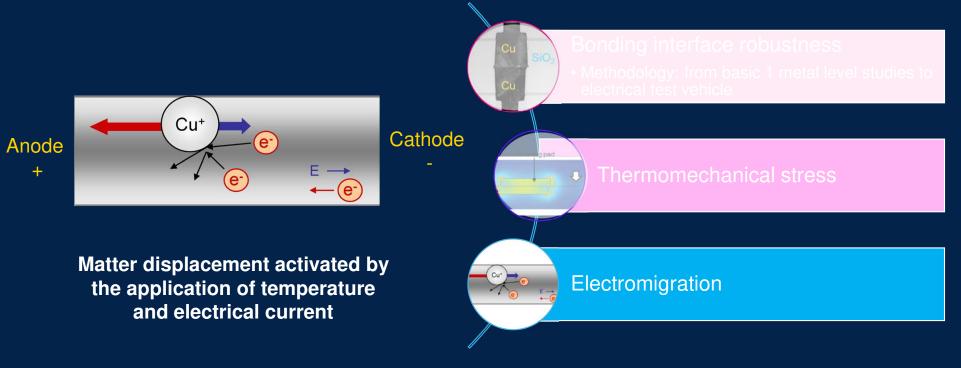

# **Electromigration**

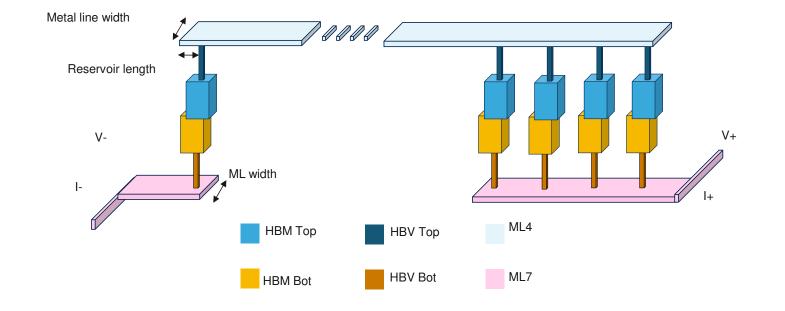

# Electromigration test structures

**NIST structures**

Slide 21 of 28

# **Electromigration tests**

(\*) S. Moreau et al., IEEE International Reliability Physics Symposium (IRPS) 2023

Lifetime is on-line with consumer specifications but identification of a modification for the failure localization with hybrid bonding pad width reduction

Slide 22 of 28

# Conclusion

# Conclusion

- Cu/SiO<sub>2</sub> hybrid bonding level is reliable for consumer applications

- Robustness demonstrated as a matter of interface stability, thermomechanical stress and electromigration

- Non-typical behavior compared to a standard back-end of line

- Barrier at Cu/SiO<sub>2</sub> is achieved with self formed Cu<sub>2</sub>O

- Modified TTF model with 1/E relation

- Contribution of the hybrid bonding interface as potential failure mode under electromigration stress

- Hybrid bonding with sub-1µm pad still leads to reliable devices

- No impact of pad microstructure modification

- Lifetime is not modified by the electromigration mechanism

Hybrid bonding stacking is mature for:

- Very high interconnection by pitch reduction

- Heterogeneous integration

Slide 24 of 28

This work has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826600 (project VIZTA)

It was also supported by the cooperative Research & Development program "IPCEI, Nano 2022 and by the French National Research Agency (ANR) under the "Investissements d'avenir" programs: ANR 10-AIRT-0005 (IRT NANO-ELEC)

# Our technology starts with You

© STMicroelectronics - All rights reserved.

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <u>www.st.com/trademarks</u>. All other product or service names are the property of their respective owners.