# **IRSP 2023**

Herzen

auf.

lüren

auf

FinFETs: Sensing and Feeling Mechanical Stress

Ingrid De Wolf \* and Vladimir Cherman imec, Belgium \* also at KU Leuven Belgium

## Introduction

#### Piezoresistive effects in metals (1856 - 1935) Lord Kelvin (1856), Cookson (1935)

1856: Lord Kelvin first reported that the resistance of iron and copper changes with elongation

Which was a problem for telegraph wire signal propagation. Studying that made him rich and famous.

That problem is solved now...

1935: Cookson first applied the term 'piezoresistance'

#### ເງຍອ

#### Piezoresistive effect in Si and Ge (1953) Smith

- Mechanical stress affects the mobility of carriers: changes the resistivity

- The relation between resistivity,  $\rho$ , and stress,  $\sigma$ , in silicon and germanium (diamond lattice) is commonly described by the piezo-resistivity tensor ( $\pi_{ij}$ )

| $\frac{1}{\rho}$ | $\begin{array}{c} \Delta \rho_{11} \\ \Delta \rho_{22} \\ \Delta \rho_{33} \\ \Delta \rho_{12} \\ \Delta \rho_{23} \end{array}$ | = | π <sub>12</sub><br>0<br>0 | $\pi_{12}$ | $\pi_{11} \\ 0 \\ 0$ | $egin{array}{c} 0 \\ 0 \\ 0 \\ \pi_{44} \\ 0 \\ 0 \end{array}$ | $\begin{array}{c} 0\\ 0\\ \pi_{44} \end{array}$ | 0<br>0<br>0<br>0 | $\begin{bmatrix} \sigma_{11} \\ \sigma_{22} \\ \sigma_{33} \\ \tau_{12} \\ \tau_{23} \end{bmatrix}$ |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|---|---------------------------|------------|----------------------|----------------------------------------------------------------|-------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|

|                  | $\Delta \rho_{13}$                                                                                                              |   | 0                         | 0          | 0                    | 0                                                              | 0                                               | $\pi_{44}$       | $ 	au_{13} $                                                                                        |

#### • For example

$$\begin{split} &\Delta \rho_{11} / \rho = \pi_{11} \sigma_{11} + \pi_{12} \sigma_{22} + \pi_{12} \sigma_{33} \\ &\Delta \rho_{22} / \rho = \pi_{12} \sigma_{11} + \pi_{11} \sigma_{22} + \pi_{12} \sigma_{33} \end{split}$$

This equation was used by Smith: he measured stress induced changes in resistance.

PHYSICAL REVIEW

Piezoresistance Effect in Germanium and Silicon

CHARLES S. SMITH Bell Telephone Laboratories, Murray Hill, New Jersey (Received December 30, 1953)

Uniaxial tension causes a change of resistivity in silicon and germanium of both *w* and *g* types. The complete tensor piezoresistance has been determined experimentally for these materials and expressed in terms of the pressure coefficient of resistivity and two simple shear coefficients. One of the shear coefficients for each of the materials is exceptionally large and cannot be explained in terms of previously known mechanisms. A possible microscopic mechanism proposed by C. Herring which could account for one large shear constant is discussed. This so called electron transfer effect arises in the structure of the energy bands of these semiconductors, and piezoresistance may therefore give important direct experimental information about this structure.

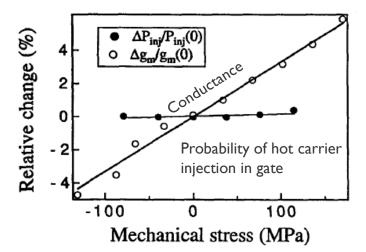

# Early experiments @ imec (1993)

Impact of stress on gate oxide reliability

Focus on hot carrier degradation (R. Bellens, R. Degraeve, I. De Wolf)

No effect on interface trap density or nr. of trapped carriers/area (in the range +-100 MPa) All effects are caused by mobility changes due to the **piezoresistance**

#### source drain n +++++ Si P nMOS

Instrumentation:

#### ເງຍອ

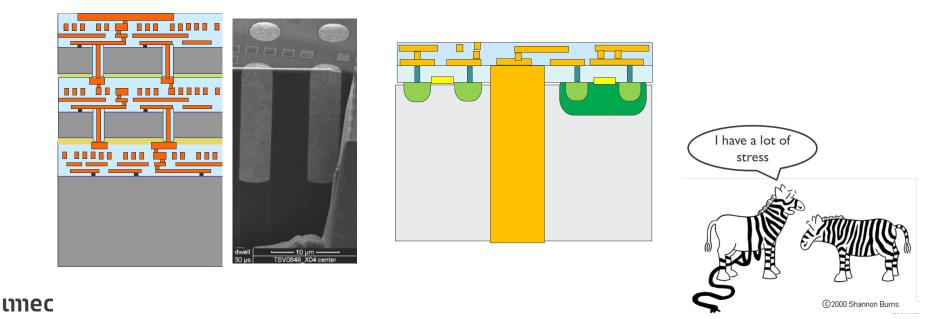

#### **3D program at imec (2006)** Through Si vias (TSV)

- Concern: Cu TSVs induce stress in Si

- This is expected to affect nearby transistors (piezoresistance effect).

Questions: How large is this effect? Should transistors stay a certain distance from the TSV?

FETs feeling stress TSV keep-out zone

#### TSVs keep-out-zone

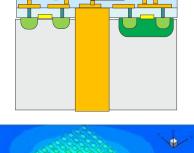

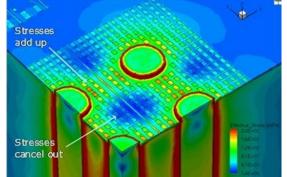

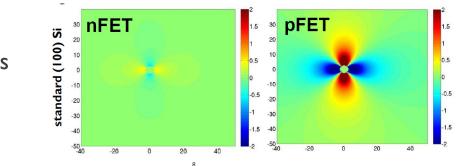

Simulations

Simulations based on Smith data: impact stress on pFET> nFET

## TSVs keep-out-zone

How to measure this in a transistor? Measure  $I_{on}$

Stress: mobility change (piezoresistance)  $\Rightarrow$   $I_{on}$  change

$\pi_{12}$  $\pi_{12}$  $[\Delta \rho_{11}]$  $\begin{vmatrix} \pi_{12} & \pi_{11} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{11} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{12} & \pi_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & \pi_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & \pi_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & \pi_{44} \end{vmatrix} \begin{bmatrix} \sigma_{11} \\ \sigma_{22} \\ \sigma_{33} \\ \tau_{12} \\ \tau_{23} \\ \tau_{13} \end{bmatrix}$  $\pi_{11}$  $\left[ \sigma_{11} \right]$  $\Delta \rho_{22}$  $\Delta \rho_{33}$  $\Delta \rho_{12}$  $\Delta \rho_{23}$  $\Delta \rho_{13}$

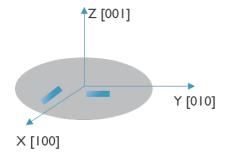

In the [110], [-110], [001] system (devices // [110] directions)

$\frac{\left[ \Delta \rho^{s}_{11} \right]}{\left[ \Delta \rho^{s}_{22} \right]}_{\Lambda = s} = \begin{bmatrix} \frac{1}{2} (\pi_{11} + \pi_{12}) + \frac{1}{4} \pi_{44} & \frac{1}{2} (\pi_{11} + \pi_{12}) - \frac{1}{4} \pi_{44} & \pi_{12} & 0 & 0 & 0 \\ \frac{1}{2} (\pi_{11} + \pi_{12}) - \frac{1}{4} \pi_{44} & \frac{1}{2} (\pi_{11} + \pi_{12}) + \frac{1}{4} \pi_{44} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{12} & \pi_{11} & \pi_{44} & 0 & 0 \end{bmatrix}$  $\begin{bmatrix} \sigma^{s}_{11} \\ \sigma^{s}_{22} \\ \sigma^{s}_{33} \\ \tau^{s}_{12} \end{bmatrix}$ 0 0  $\tau^{s}_{23}$  $\tau^{s}_{13}$ 0  $\Delta \rho^{s}_{13}$  $\pi_{44}$ 0 0  $2(\pi_{11} - \pi_{12})$

In practice, the following relation is used at imec:

|   | $\Delta I_{11}$ |   | $\pi'_{11}$ | $\pi'_{12}$ | $\pi'_{12}$   | $0 \\ 0 \\ 0 \\ \pi'_{44}$ | 0           | 0           | [ <b>σ</b> <sub>11</sub> ]                         |

|---|-----------------|---|-------------|-------------|---------------|----------------------------|-------------|-------------|----------------------------------------------------|

|   | $\Delta I_{22}$ |   | $\pi'_{12}$ | $\pi'_{11}$ | $\pi'_{12}$   | 0                          | 0           | 0           | $\sigma_{22}$                                      |

| 1 | $\Delta I_{33}$ | _ | $\pi'_{12}$ | $\pi'_{12}$ | ${\pi'}_{11}$ | 0                          | 0           | 0           | $\sigma_{33}$                                      |

| Ι | $\Delta I_{12}$ | - | 0           | 0           | 0             | ${m \pi'}_{44}$            | 0           | 0           | $ 	au_{12} $                                       |

|   | $\Delta I_{23}$ |   | 0           | 0           | 0             | 0                          | $\pi'_{44}$ | 0           | $egin{array}{c c} 	au_{23} \ 	au_{13} \end{array}$ |

|   | $\Delta I_{13}$ |   | 0           | 0           | 0             | 0                          | 0           | $\pi'_{44}$ | $ \tau_{13} $                                      |

These coefficients are NOT the piezoresistance coefficients.

They are related to the inverse tensor (related to piezoconductivity instead of piezoresistivity)

ເກາຍc

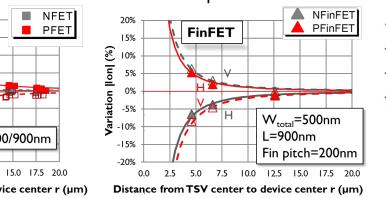

## TSVs keep-out-zone

ເກາຍc

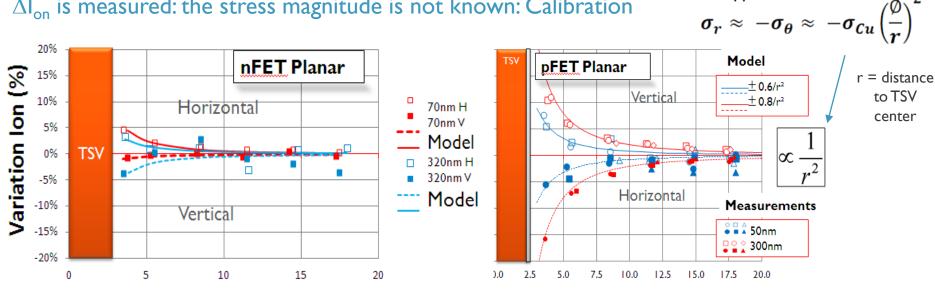

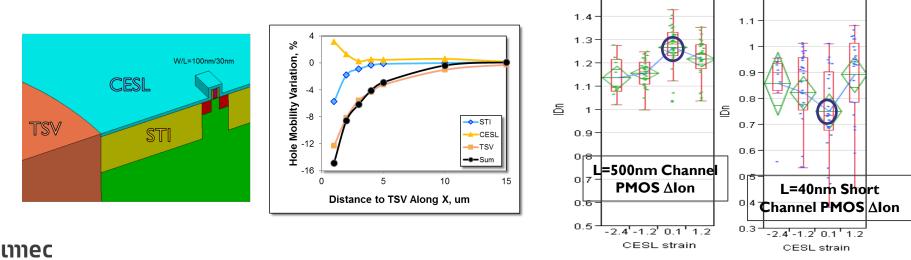

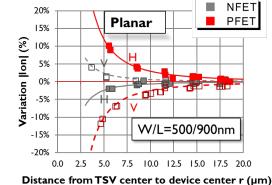

Experiments (planar FETs at different distances from TSV)

- Planar FETs are indeed stress sensitive

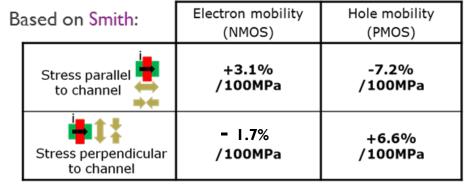

- PFET is more sensitive than NFET: confirms Smith data

- $\Delta I_{on}$  is measured: the stress magnitude is not known: Calibration

#### Distance from TSV center to device center (µm)

| B | ased on Smith:                     | Electron mobility<br>(NMOS) | Hole mobility<br>(PMOS) |  |  |

|---|------------------------------------|-----------------------------|-------------------------|--|--|

|   | Stress parallel                    | +3.1%<br>/100MPa            | -7.2%<br>/100MPa        |  |  |

|   | Stress perpendicular<br>to channel | - I.7%<br>/100MPa           | +6.6%<br>/100MPa        |  |  |

Lamé approximation:

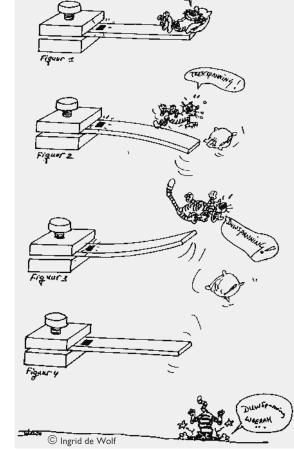

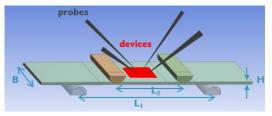

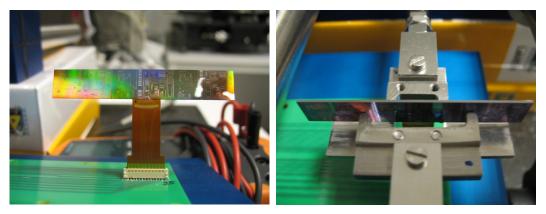

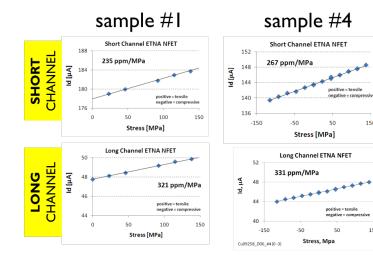

### Calibration Calibration: 4-point bending

4-point bending

Delaminator DTS Company (Reinhold Dauskardt)

Applied stress ranges between -150 MPa to + 150 MPa (risk for die cracking at higher stress)

And many more experiments...

#### TSV-stress impact depends on technology

- Smidt's numbers (from 1953) are commonly used as of piezo-resistive components

BUT: results from external applied stress using 4-point bending gives different results for more modern technologies.

- Simulations and experiments indicate that TSV impact (so, stress impact) depends on strain in the channel

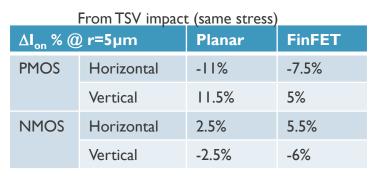

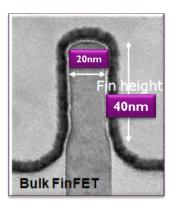

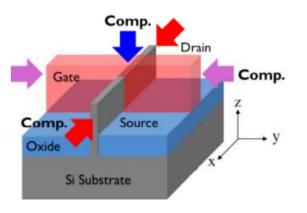

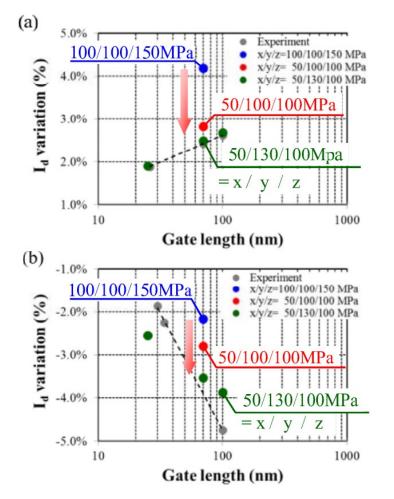

## Planar FET versus FINFET

Using TSV induced stress

- Also FINFETS are sensitive to stress

- Planar: N type less sensitive than P type (from TSV proximity impact on lon (at 5 µm from a TSV))

- Bulk Si FinFET: Both N and P type are sensitive (confirmed by TCAD)

- The impact of stress decreases with decreasing channel length for both planar and finFET

Measurements on wafers with 5x50µm TSV

#### ເງຍອ

FETs feeling stress Out-of-plane stress

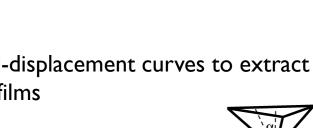

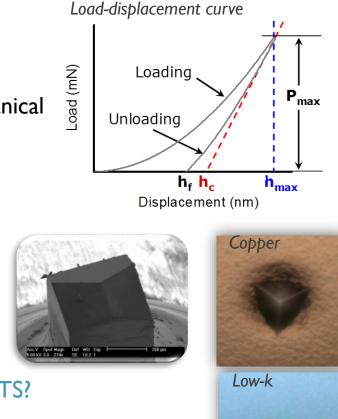

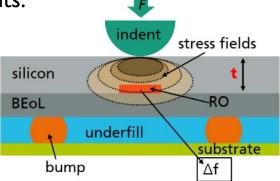

## Nanoindentation

Materials focus

- Measures load-displacement curves to extract mechanical • properties of films

- Hardness •

- Elastic modulus •

- Fracture toughness ٠

- . . .

- Nanoindentation uses well defined tips ٠ (Berkovich, cube corner, spherical)

Can this be used to study impact of vertical stress on FETS?

Film

Substrate

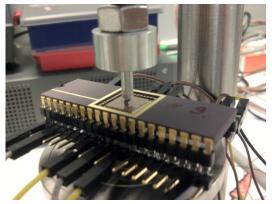

# First experiments (2013)

Push on a packaged chip (need electrical access)

vertical stress affects planar nFETS (PTCQ test chip)

Delaminator DTS Company (Reinhold Dauskardt) (2004)

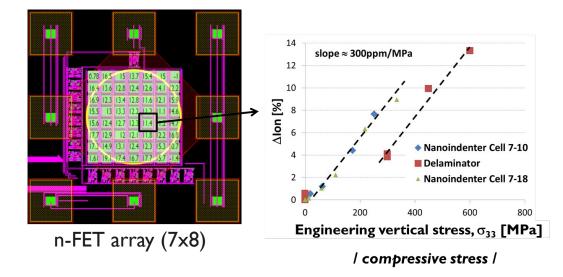

# nFET' vertical gauge factor $\approx$ -300ppm/MPa Imec

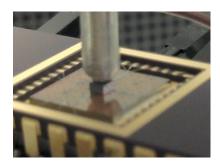

## Nanoindentation + in-situ probing

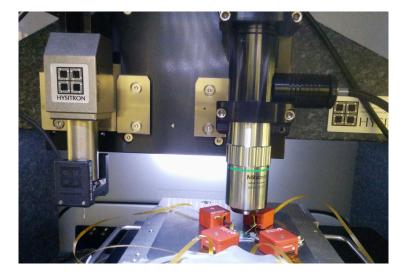

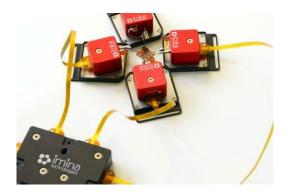

- Use the nanoindenter (Hysitron (Bruker)) to apply out-of-plane stress on a device

- Imaging mode can be used to 'find' the device and check the position where stress was applied

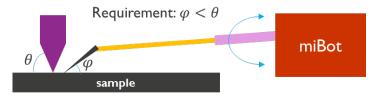

- Add small probes (miBot, imina technologies) for in-situ probing

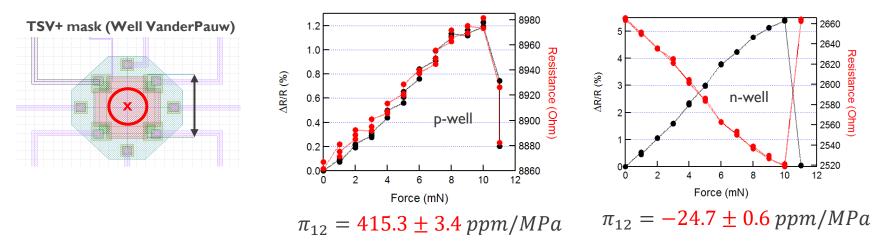

## Out-of-Plane Stress impact

Resistor

Clear increase of the resistance with force for the p-well, and (larger) decrease for the nwell device: functionality of the set-up demonstrated

- FEM used to calculate applied stress from indentation force

- Determination of piezo-resistance coefficient (out-of-plane): good correspondence with theory (534 and -11 respectively)

Imec

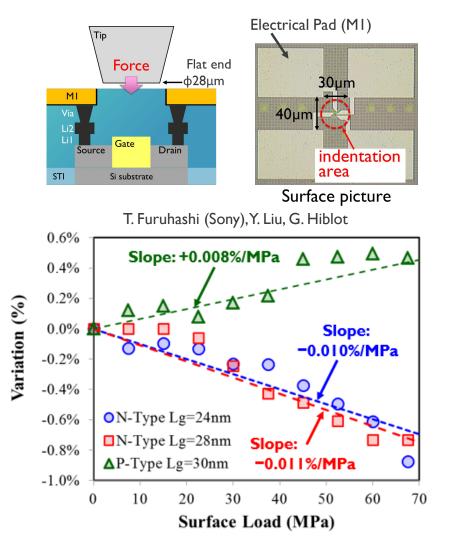

## Out-of-Plane Stress impact FINFETS (28 nm node)

Clear impact of out-of-plane force

- I<sub>d</sub> of N-Type decreases with increasing force

- I<sub>d</sub> of P-Type increases with increasing force

- Sensitivity decreases with decreasing gate length

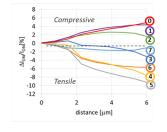

#### Out-of-Plane Stress impact FINFETS (28 nm node)

BUT: Vertical force also induces in-plane compressive stress (FEM simulations). For a vertical force (z) of 200 mN: Larger stress  $\perp$  FIN (y) than // FIN (x) (due to stiffer gate material)

#### ເງຍອ

## Alternative method

S. Schlipf PhD Thesis, TU Dresden, 2021

How to distinguish impact of different stress components:

9

IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 21, NO. 1, MARCH 2021

#### Stress-Induced Transistor Degradation Studied by an Indentation Approach

S. Schlipf<sup>®</sup>, A. Clausner, J. Paul, S. Capecchi, L. Wambera, K. Meier, and E. Zschech

## Impact of stress on...

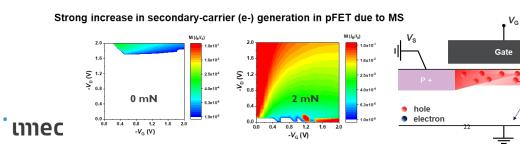

Using Hysitron/Mibot combination

secondary

e-h pairs

- BAPSI test/shear stress: Kris Vanstreels

- 3D memory devices: Anastasiia Kruv (PhD)

- FINFETS: Takahisa Furuhashi (Sony)

- HBT, BJT, bandgap reference circuit: Yefan Liu, Gaspard Hiblot

- Silicide contact resistivity: Yefan Liu, Gaspard Hiblot

- MOSFET local: Kookjin Lee (post doc)

- Reliability ...

#### Locally induced MS up to **GPa** level Diamond Stress field

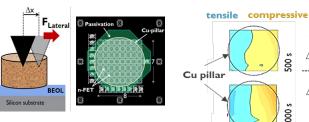

FETS sensing stress CPI

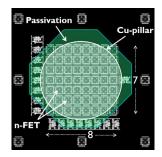

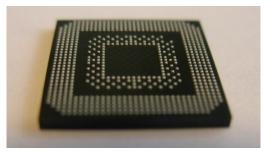

#### **Test structures**

- FETS are sensitive to stress: Can be used as stress sensor

- Various test-chips were developed at imec over the years, containing local and global 'stress' sensors

n-FET array (7x8)

Negative current shift indicating compressive stress from shrinking overmold

ເງຍອ

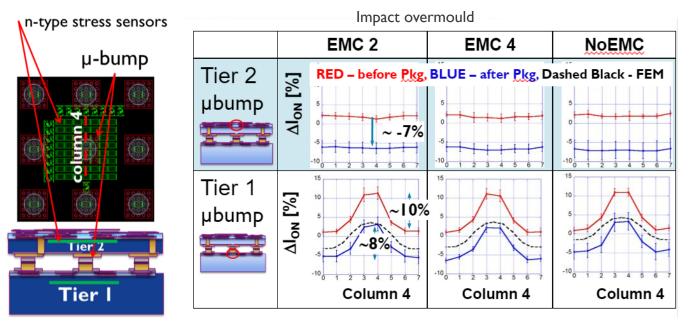

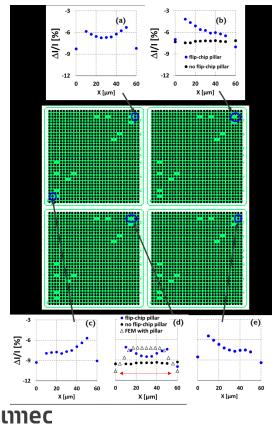

## Stress around µ-bump (sensor array) Cherman ECTC 2015

Packaging has a large effect on  $I_{ON}$ Local shape at  $\mu$ -bump is preserved.

#### ເກາec

#### Global and local stress in flip-chip BGA package Cherman EMPC2019

ເກາຍc

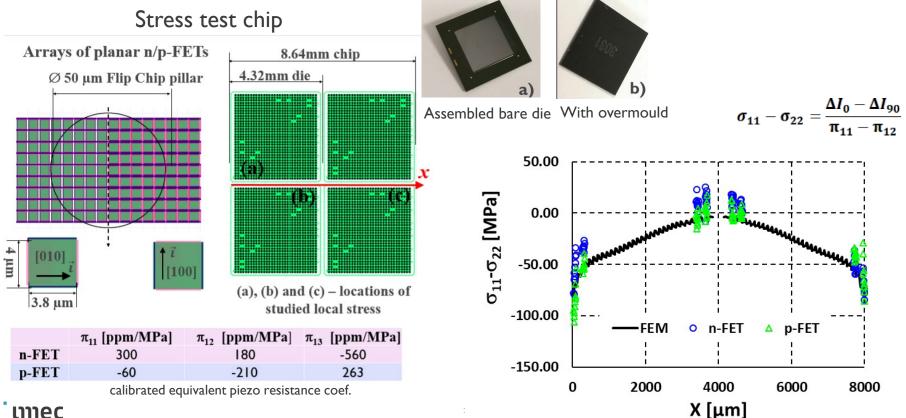

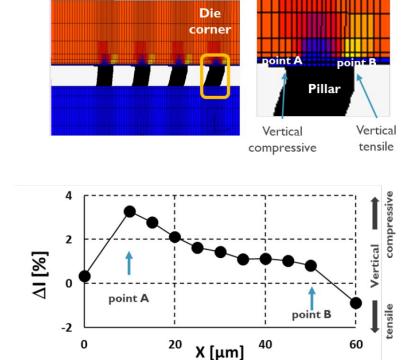

## Global and local stress in flip-chip BGA package Cherman EMPC2019

Electrical response of n-type stress sensors at different locations on the packaged test chip.

Response above pillars at the corner of the packaged die

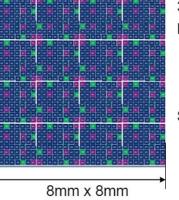

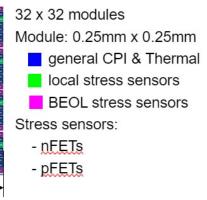

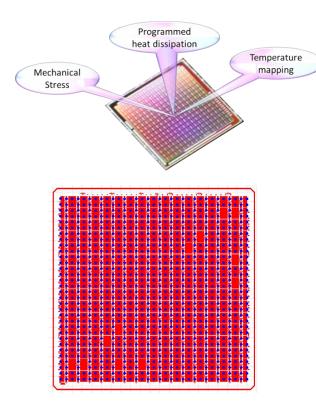

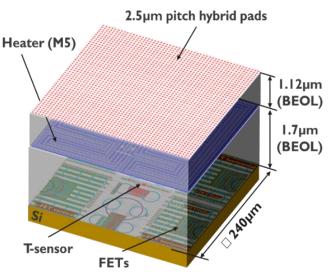

## Test chip

Test Chip consisting of 4.32 X 4.32  $mm^2\,squares$  contains 256 unit cells 240x240 $\mu m^2$

#### Every unit cell contains

- temperature sensor

- programmable heater

- stress sensors

- 744 FEOL (FETs)

- 2 BEOL (capacitive)

Chips are compatible with:

- Variable chip size: 4x4 mm<sup>2</sup> 30x20 mm<sup>2</sup>

- Flip-Chip, wire-bond and fan-out packaging options

- Different 3D integration schemes (3DSIC, 3DSOC, 3D interposer) including N>2

# Conclusions

# Stress: A never ending story in microelectronics.

## Acknowledgements

Thank you to all imec contributors and all partners of the 3D program of imec.

Special thanks to all design and processing engineers providing samples and all imec stress-impact researchers:

Eric Beyne, Vladimir Cherman, Wei Guo, Ibnea Sina Bony, Alireza, Rouhi Najaf Abadi, Yefan Liu, Anastasiia Kruv, Ben Kaczer, Geert Van der Plas, Gaspard Hiblot, Mario Gonzalez, Robin Degraeve, Rudy Bellens, Takahisa Furuhashi (Sony), Kris Vanstreels, ...

Special thanks to Bruker (Hysitron) and Imina